主题中讨论的其他器件:DS16F95QML、

您好!

1. 禁用驱动器和接收器时 DS16F95QML 的功耗是多少?

2. 当驱动器正在运行但接收器被禁用时、DS16F95QML 的功耗是多少?

3.当接收器正在运行但驱动器被禁用时,DS16F95QML 的功耗是多少?

4. 当两个接收器均为驱动器运行时,DS16F95QML 的功耗是多少?

此致、

Rajan。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

1. 禁用驱动器和接收器时 DS16F95QML 的功耗是多少?

2. 当驱动器正在运行但接收器被禁用时、DS16F95QML 的功耗是多少?

3.当接收器正在运行但驱动器被禁用时,DS16F95QML 的功耗是多少?

4. 当两个接收器均为驱动器运行时,DS16F95QML 的功耗是多少?

此致、

Rajan。

您好、Rajan、

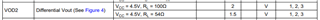

1. 禁用驱动器和接收器时 DS16F95QML 的功耗是多少?

A:在 VCC = 5.5V 时、在接收器和驱动器功能均被禁用的情况下、此器件将汲取最大25mA 的电流。

![]()

2. 当驱动器正在运行但接收器被禁用时、DS16F95QML 的功耗是多少?

3.当接收器正在运行但驱动器被禁用时,DS16F95QML 的功耗是多少?

答:要回答问题2和3、很难回答。 电流消耗将介于25mA 和28mA 之间。 通常、当驱动器在禁用接收器的情况下运行时、与接收器在禁用驱动器的情况下运行时相比、您会看到更多的电流消耗。 确定的唯一方法是在触发/RE 和/DE 条件时对测量 ICC @ VCC = 5.5V 的该器件进行基准测试。

4. 当两个接收器均为驱动器运行时,DS16F95QML 的功耗是多少?

A:在 VCC = 5.5V 时、当接收器和驱动器功能均被启用时、此器件将汲取最大28mA 的电流。

![]()

此致、

Tyler

您好、Rajan、

要回答有关 VCC 和 GND 之间连接的去耦电容器的问题、这取决于您的传入电源对收发器的噪声。 通常、0.01uF、0.1uF、1uF 等可用于滤除高频噪声。 将这些电容器尽可能靠近 VCC 引脚放置、以便在为收发器供电之前清理电源线。

这是一款符合 RS422/485标准的器件、此器件符合 EIA 标准。 您可以预期 RS422/485差分信号出现在引脚 A 和 B 上、这需要引脚 A 和 B 之间的端接电阻器。理想情况下、选择等于、 或者最好比电缆的特性阻抗(Zo)高10%、以消除反射、从而实现更高的数据速率和更长的电缆长度。 以下是描述不同端接技术的应用手册:

https://www.ti.com/lit/an/snla034b/snla034b.pdf

在逻辑接收侧引脚 RO 上、包含一个连接到 VCC 的弱上拉电阻器将接收总线保持在 MCU 的已知状态将会有所帮助。 如果/RE 为高电平、则接收器将关闭、如果没有上拉电阻器、MCU 上的 RxD 引脚将保持悬空。

CTS 和 RTS 引脚可能连接到 DS16F95QML 使能输入的使能输入。 RS422/485不具有流控制、而是由您的设计在物理和软件方面控制 多个器件之间的通信流。 这可以是通过向使能引脚发出信号来控制收发器之间通信流的一种方法。

此致、

-Tyler

将 RTS 连接到 RE 和 DE 输入以控制半双工通信可能更简单?

关于端接、下面的文章很有意思: 如何正确配置和导线 RS-422和 RS-485网络-密封层

Rajan、

如果将 RTS 连接到 RE 和 DE 输入、则可以控制驱动器和接收器何时同时打开或同时关闭。 您无法单独控制设备的驾驶或接收部分。 如果这适用于您的应用、那么这似乎是一个合理的解决方案。 请记住、如果您使用的是半双工通信、那么您只在一个时间点进行传输或接收。 由于采用半双工配置、因此无法同时发送和接收数据。 通过将 RTS 连接到 RE 和 DE 输入、器件的一侧、无论是驱动器还是接收器、都将空闲、即使当前未使用、也将消耗功率。

此致、

Tyler

Rajan、

我相信 RS485器件的标准是能够在54欧姆负载上驱动1.5V 差分信号、DS16F95QML 是为这种负载而设计的。

请注意、如果在传输线路的两端端端端进行端接、则负载电阻的影响将减半。 示例:接收侧为100 Ω、发送侧为100 Ω= 100 Ω|| 100 Ω= 50 Ω、超出标准规格。 最好在两端使用200欧姆电阻器进行端接、这样、如果适合您的应用、组合负载将被视为100欧姆。

在 RO 上使用1k Ω- 10k Ω 上拉电阻器来限制瞬态事件期间的噪声电流。

此致、

Tyler