主题中讨论的其他器件:TCA39306

您好!

我使用 TCA39306作为 I2C 开关、配置中 VCC1=VCC2=VREF1=VREF2=3.3V。

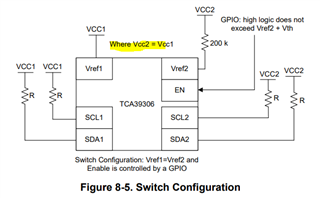

理想情况下、我的使能引脚需要使用3V3电压进行控制、在这种情况下不会受到以下限制: Vcc2 >= Vref1 + 0.7V、并且我将具有 VCC1=VCC2=VREF1 =VREF2=VREF2=VREF2=VENAB=3.3V、在这种配置中、开关将不工作。

这是正确的吗?

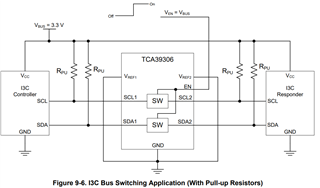

以下解决方案能否在我的用例中正常工作:

我是否可以为 I2C 总线使用以下架构? 如果是,我的 I2C 总线对于 SDA 引脚是否仍然是双向的?

此致、