主题中讨论的其他器件: DS90UH941AS-Q1

对于 DS90UB941AS-Q1或 DS90UH941AS-Q1串行器器件、DSI 或 REFCLK 输入抖动的测量方法是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

对于 DS90UB941AS-Q1或 DS90UH941AS-Q1串行器器件、DSI 或 REFCLK 输入抖动的测量方法是什么?

DS90UB941-Q1/DS90UH941AS-Q1的抖动要求取决于器件所用的工作模式。 需要考虑的两种主要模式为:

- DSI 参考时钟模式-来自视频源的 DSI 时钟用作串行器器件的参考时钟。 串行器无需外部振荡器或晶体输入

外部 REFCLK 模式- DSI 时钟仅用于为器件的视频输入计时、但不用作串行器的参考时钟。 在此模式下、必须以与视频像素时钟相同的频率将外部 REFCLK 连接到串行器 REFCLK 输入

----------------------------------------------------

在 DSI 参考时钟模式下、DSI 时钟输入抖动要求至关重要、因为 DSI 时钟用于为运行速度远高于 DSI 输入的 FPD III 串行器提供时钟源。

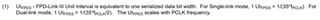

在单 FPD-Link III 模式下,FPD-Link 速率为 fDSI*(N/12)*35,其中 N 是 DSI 通道数,fDSI 是以 MHz 为单位的 DSI 时钟频率。

在双 FPD-Link III 模式下,FPD-Link 速率为每个 FPD-Link 通道的 fDSI*(N/12)*(35/2)

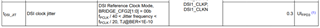

由于 FPD-Link III UI 远小于 DSI 时钟的 UI、DSI 时钟的抖动贡献会按比例影响 FPD III 时钟的抖动、因此 DSI 时钟抖动是根据 FPD3 UI 而不是 DSI 时钟 UI 指定的。 在此模式下、DSI 时钟抖动的要求为:

例如、当 PCLK 为148.5MHz、双 FPD-Link 且使用4个 DSI 通道时、fDSI 将为148.5*(12/4)= 445.5MHz。 DSI 时钟抖动要求为:

(1/(35*148.5MHz/2)*0.3 = 115ps

----------------------------------------------------

在外部参考时钟模式下、DSI 时钟抖动不具有与 FPD III UI 直接相关的时序要求、因为它不用于直接提供 FPD III 时钟。 外部参考时钟模式下的 DSI 时钟要求仅基于 MIPI DPHY 规范中的标准时序要求。 在此模式下、应根据数据表要求表中的要求表征 REFCLK 输入抖动:

例如、当 PCLK 为148.5MHz、双 FPD-Link 且使用4个 DSI 通道时、fDSI 将为148.5*(12/4)= 445.5MHz。 外部 REFCLK 频率为148.5MHz、 REFCLK 时钟抖动要求为:

(1/(35*148.5MHz/2)*0.28 = 108ps

----------------------------------------------------

DS90UB941AS-Q1/DS90UH941AS-Q1抖动要求适用于总抖动(TJ@BER): https://www.ti.com/lit/pdf/SCAA120B

为了表征总抖动、TI 建议 使用配备了 DPOJET 等抖动分析程序的高速示波器来测量 TJ@BER。 DPOJET 测量中使用的时钟恢复设置旨在匹配串行器件的输入 PLL 特性:

-方法= PLL 自定义 BW

PLL 类型= II 类

-双路 FPD-Link 的环路 BW = f/40 (其中 f = PCLK)

-单个 FPD-Link 的环路 BW = f/20 (其中 f = PCLK)

-阻尼= 2

-目标 BER = 1e-10

高通滤波器:无

-低通滤波器:一阶 、f/20用于双路 FPD-Link (其中 f = PCLK)

-低通滤波器:一阶 、针对单个 FPD-Link 的 f/10 (其中 f = PCLK)