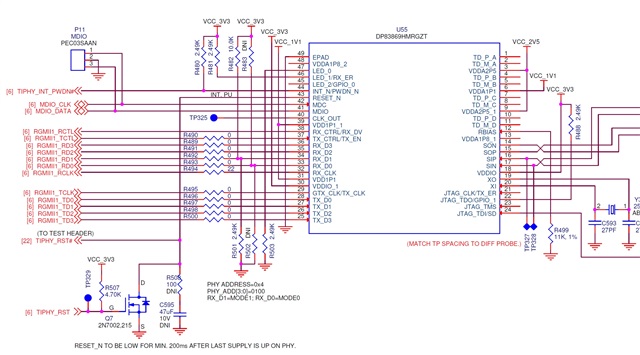

主题中讨论的其他器件:DP83869、

我们在 AM335x 和1G SFP 之间使用 DP83869。 在 SFP 侧、链路正在建立。 但是、AM335x 的 SGMII 接口无法正常工作。

我注意到、DP83869中的 GEN_STATUS1寄存器为0、表示"本地接收器不正常"和"远程接收器不正常"。

第一个问题:什么会使它们"不好"?

RGMII_CTRL 为0x00d0、表示发送和接收时钟相对于数据移位。 我已经在 ANA_RGMII_DLL_CTRL 中尝试了多个值、分别是 DLL_TX_DELAY_CTRL_SL 和 DLL_RX_DELAY_CTRL_SL。

第二个问题: 延迟值 DLL_TX_DELAY_CTRL_SL 和 DLL_RX_DELAY_CTRL_SL 是什么(介于什么和什么之间)? 说明表示它们影响 CLK_90、但 CLK_90不会出现在数据表的其他位置。

如果它有影响: 1G SFP 线侧是连接到交换机的 RJ45铜质连接。 CFG_OPMODE 为1。 尽管交换机支持1G,但该链路正在协商为100/Half。 这会导致 AM335x 侧将 Tx RGMII 时钟设置为25MHz、而来自 PHY 的 RX 时钟设置为125MHz。

谢谢、

Steve