主题中讨论的其他器件:TCA9517

尊敬的团队:

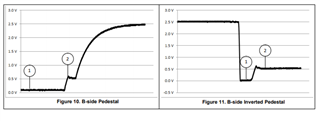

请参阅底座/倒置底座、了解一些问题。

1.反向底座的"持续时间"是否固定? SCLB/SDAB 保持 GND 的时间(图11) 在打开 VOL 之前的短时间内、该持续时间的特征是什么?

2. 可以接受多大的过冲? 过冲的峰值电压与 VCCB 之间是否存在任何关系?

谢谢

法尔曼

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Farman、

1.在反相基座期间、器件 B 侧接地的持续时间很可能是固定的时间。 但是、我们尚未确定该器件的时间、因此我不确定。

该器 件可在高达1MHz 的频率下运行、因此您可以确保它位于地面的时间足够短、不会在1MHz 下影响运行。

2.当你谈论过冲时,我假设你在讨论下图中的第2点:

一般来说、过冲不会是问题。 只有当反相基座超过连接到 TCA9517 B 侧的器件的 VIL 时、才会出现问题。 只要过冲低于连接到 TCA9517 B 侧的 I2C 器件的 VIL、就不会出现任何问题。 如果您希望尽可能减少过冲、则应确保 B 侧使用的上拉电阻器允许超过20ns 的上升时间。 如果上升时间过短、则会导致过冲电压。

最棒的

Chris