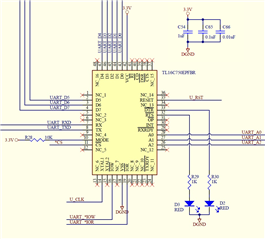

Other Parts Discussed in Thread: TL16C750E

我很难让 TL16C750E UART 正确读取数据。

问题似乎出在内部缓冲区中。

背景:

测试代码正在将器件初始化为在非 FIFO 轮询模式下运行、奇偶校验位代码控制9位数据运行。

如果以下初始化顺序不正确、请告诉我如何纠正它:

复位(50us 高脉冲)

LCR <- 0xBF

EFR <-- 0x10

LCR <-- 0x83

DLH <-- V1 ----+

dll <-- V2 |-->1M 波特

DLF <-- V3 ----+

LCR <-- 0xBF

EFR <-- 0x00

LCR <-- 0x03

IER <-- 0x00

FCR <-- 0x00

一个独立的电路板以低速率发送递增(1)字节值(9位数据)(所以运行时数据没有问题)、并且它的代码一直首先启动。

在上述初始化之后、TL16C750E 测试代码向该电路板发送一个值以触发它开始发送其慢速数据、然后轮询 LSR 的位0、查找新接收到的字节:

读取 LSR、直到 THR 空为真。

MCR <-- 0x02 (/DTS 和/RTS 输出驱动 LED)

LCR <- 0x2B (通过代码控制的奇偶校验位传输9位数据)

THR <-触发响应的数据

count=0 log 检测接收到的新字节

永久循环:

读取 LSR 直到"接收器中的数据"位=1

如果为 true

递增计数

读取数据字节的 RHR

如果 数据>0

记录数据

记录 count 的值

字节序

字节序

死循环结束

我在日志结果中看到的是:

真正 的数据直到读取128个字节后才开始。 注意: LSR" 接收器中的数据"位每次都正确更新。

前64位始终为0x00、后64位不正确、第二64位的第一个字节关闭、例如、当真实数据为0x05时、0xC5在后续字节上从0xC5递增。

2.如果另一个电路板的起始值发生更改、则第128个读取值在以下情况下才正确:

a:TL16C750E 测试代码运行两次

b.对 TL16C750E 电路板进行下电上电。

目的是让 UART 在非 FIFO 的轮询模式下运行,因此根据数据表:"如果 FIFO 被禁用,FIFO 的位置0被用来存储字符"(第9.2.2节)

但存储和读取内部指针似乎仍然使用整个128字节 FIFO、而不是仅使用位置0来存储和读取数据。

提前感谢您的帮助。