主题中讨论的其它部件:SN65DSI84、DSI 调谐器

您好、TI 支持团队、

目前、我们正在开发一种集成了 SN65DSI84-Q1的新设计、SN65DSI84的 I2C 配置存在一些问题、这些问题适用于我们连接的双 LVDS 面板。

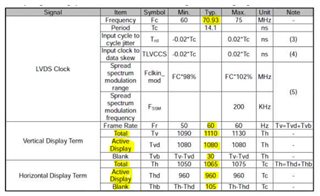

我们使用15.6英尺的双 LVDS 面板(分辨率1920 RGB x 1080)和以下时序参数、您可以在此消息附件(Panel.jpg)中看到这些参数。 还随附面板数据表!

对于 SN65DSI84的以下 I2C 配置、我们在 TFT 面板上获得了有效的测试模式。

我们的配置寄存器值:

REG=0x0a 值=0x85

=> HS_CLK_SRC=LVDS 像素时钟取自 MIPI D-PHY 通道 A

=> LVDS_CLK_RANGE=010–62.5MHz≤LVDS_CLK < 87.5MHz

=> PLL_EN_STAT=1 - PLL 被启用

REG=0x0B value=0x28 => DSI_CLK_divider = 00101–6分频

REG=0x0d Value=0x01 => PLL_EN=1–PLL 被启用

REG=0x10 value=0x26 => Cha_DSI_lane = 00–启用四个通道

REG=0x12值=0x55 => CHA_DSI_CLK_RANGE=0x55–425≤频率< 430MHz

REG=0x18值=0x0c

=> CHB_24bpp_mode=1–强制24bpp;LVDS 通道 B 通道4

=> Cha_24bpp_mode=1–强制24bpp;LVDS 通道 A 通道4

=> LVDS_LINK_CFG=0–启用 LVDS 通道 A 和通道 B 输出

=> VS_NEG_POLICITY = 0–VS 是由正极性驱动的

=> HS_NEG_POLICITY = 0–HS 是正极性驱动

=> DE_NEG_POLICITY = 0–DE 是由正极性驱动的

REG=0x1a 值=0x00

=> CHB_LVDS_TERM=0–100Ω Ω

=> CHA_LVDS_TERM=0–100Ω μ A

REG=0x20值=0xc0 (CHA_ACTIVE_LINE_LENGTH_LOW)

REG=0x21 Value=0x03 (CHA_ACTIVE_LINE_LENGTH_HIGH) =>每行960个有源像素

REG=0x24值=0x38 (CHA_竖 直显示大小_低电平)

REG=0x25 value=0x04 (Cha_vertable_display_size_high) => 1080个面板活动行

REG=0x28值=0x21 (CHA_SYNC_DELAY_LOW)

REG=0x29值=0x00 (CHA_SYNC_DELAY_HIGH)

REG=0x2C 值=0x23 (CHA_HSYNC_PULSE_WIDTH_LOW)

REG=0x2D 值=0x00 (CHA_HSYNC_PULSE_WIDTH_HIGH)

REG=0x30值=0x0a (CHA_VSYNC_PULSE_WIDTH_LOW)

REG=0x31值=0x00 (CHA_VSYNC_PULSE_WIDTH_HIGH)

REG=0x34值=0x23 (CHA_HORIZAL_BACK_STRATE)

REG=0x36值=0x0a (CHA_竖 直_后_沿)

寄存器= 0x38值= 0x23 (CHA_HORIZAL_FRONT_CRATE)

REG=0x3a 值=0x0a (Cha_Vertical _front_Porch)

REG=0x3C Value=0x10 (CHA_TEST_pattern) =>测试模式激活!!!

=>面板上的测试模式正常

=>设置寄存器= 0x3C 值= 0x00 (测试模式未激活)仅显示黑屏=>通过 MIPI-DSI 输入传输的数据不会显示在面板上

数据表第34/35页列出的寄存器配置和示例配置之间的问题(www.ti.com/.../sn65dsi84.pdf)

=>示例描述了水平活动= 1920或0x780、但对于我们来说、如果将其设置为1920/2=960 (0x3c0)、则仅在测试图形模式下工作

=>示例描述 DSI_CLK_DIVIDER = 0010b–除以6、但值0010b 不会偏离6 (RE=0x0B 显示 DSI_CLK_DIVIDER=00101–除以6)

今天、我们还使用 TI 的"DSI 调谐器"-工具对寄存器设置进行了双回声、所有设置似乎都正确(另请参阅随附的 DSI 调谐器输入和输出页面)。

您能否查看我们面板的寄存器配置中可能存在的问题、以及如何在数据表示例中解释问题?

非常感谢您的支持和反馈。

此致、

Johannes