您好、专家

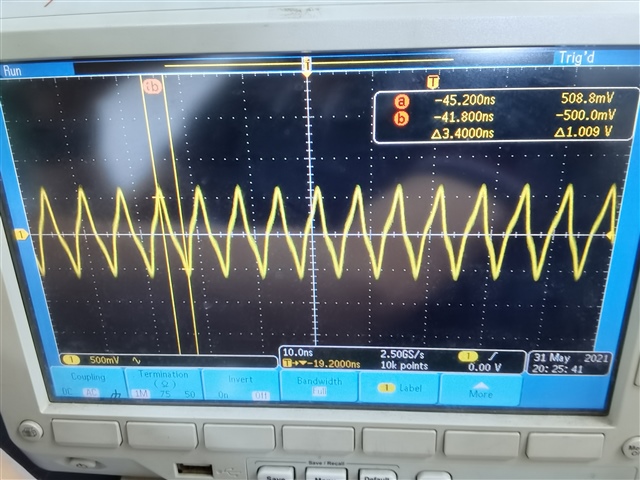

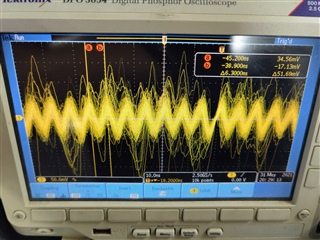

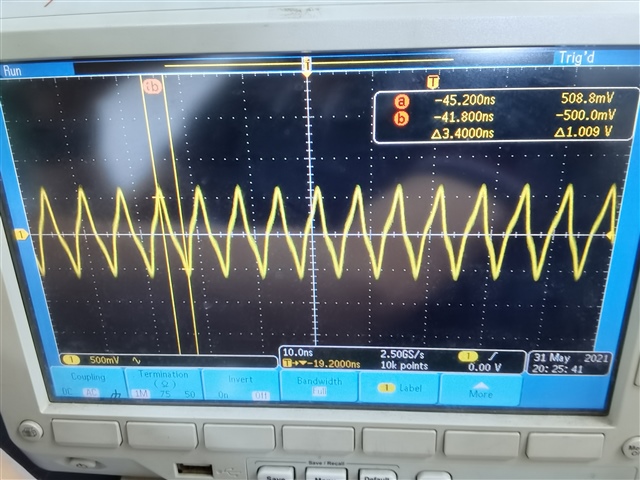

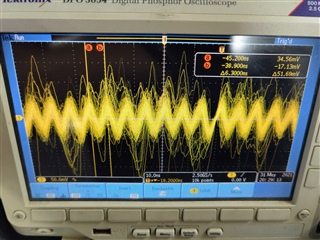

我的客户在 SN65DP159上遇到问题--时钟输出异常,请参阅随附的波形及其原理图。

此问题发生在 HDMI2.0和 HDMI1.4上、当问题发生时、HPD_SNK 为高电平。

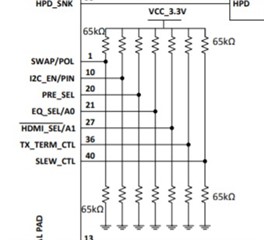

您能否帮助查看原理图并找出是否存在任何设计错误、尤其是上拉和下拉引脚?

您能否告诉客户应该使用哪对 I2C 进行调试? 谢谢。

e2e.ti.com/.../HDMI_5F00_2.0.pdf

此致。

陈

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、专家

我的客户在 SN65DP159上遇到问题--时钟输出异常,请参阅随附的波形及其原理图。

此问题发生在 HDMI2.0和 HDMI1.4上、当问题发生时、HPD_SNK 为高电平。

您能否帮助查看原理图并找出是否存在任何设计错误、尤其是上拉和下拉引脚?

您能否告诉客户应该使用哪对 I2C 进行调试? 谢谢。

e2e.ti.com/.../HDMI_5F00_2.0.pdf

此致。

陈

陈

查看原理图

1. OE 引脚上是否有外部下拉电容器? 请确保您符合 DP159的数据表中列出的上电要求。

2. 建议在输出端使用共模扼流圈以实现 EMI

您可以在正常输出情况和不良输出情况之间转储 DP159第0页和第1页寄存器吗? 第0页寄存器位于 DP159数据表中。 对于第1页寄存器、请将0x01写入寄存器0xFF、然后从0x00转储到0xB1。

您是否还可以在两块板之间交换 DP159、以查看问题出在装置还是主板?

谢谢

David

陈

1:应使用哪对 I2C 接口来写入寄存器。

*** SCL_CTL 和 SDA_CTL (引脚15和16)

2、OE 引脚上没有添加下拉电容。 该电容器的哪个功能很重要?

***请参阅第9.3.1节和9.3.2节,您需要 OE 引脚上的电容器以确保正确的上电时序

SRC、SNK 和 CTL I2C 接口的功能有何区别?

*** SCL_CTL 和 SDA_CTL ->对 DP159寄存器进行编程

*** SCL_SRC 和 SDA_SRC,DDC 总线的一部分,用于在源设备和接收设备之间通信 EDID。 根据需要连接到源极侧

*** SCL_SNK 和 SDA_SNK,DDC 总线的一部分,用于在源设备和接收设备之间通信 EDID。 必须连接到灌电流侧

谢谢

David

你(们)好、David

感谢您的回复! 还有三个问题需要您的帮助。

1.除了 OE 和共模扼流圈问题外,客户的设计还可能存在哪些设计缺陷?

2.数据表的原理图中还有一些上拉和下拉电阻器、但客户在其设计中没有为这些电阻器留出空间、这很重要吗?

3.根据您的建议,将 SRC I2C 接地并将 SNK I2C 连接到 FPGA,当 SNK 的上拉电压为5V 而 SRC 的上拉电压为3.3V 时,是否有任何问题? 是否会通过 SNK I2C 对 FPGA 施加外部干扰?

此致。

陈

陈

1.我看不到原理图有什么其他问题、但如果可能、我们还应该检查它们的布局。

2. I2C_EN 必须被拉高或拉低以在引脚搭接和 I2C 模式之间进行选择。 必须拉高或拉低 HDMI_SEL 以在 DVI 和 HDMI 之间进行选择。 其他一切都可以在其设计上保持浮动基准。

如果 FPGA 需要3.3V DDC、则需要外部电平转换器从5V DDC 转换到3.3V DDC。

谢谢

David

大家好、David

请参阅随附的 PCB 文件。

至于建议#3、我是否可以将 SRC I2C 接地、将 SNK I2C 从 HDMI 端口连接到 SN65DP159、然后通过电平转换器连接到 FPGA?

此致。

陈

陈

至于建议#3、我是否可以将 SRC I2C 接地、将 SNK I2C 从 HDMI 端口连接到 SN65DP159、然后通过电平转换器连接到 FPGA?

有关 DDC 侦听实现、请参阅以下方框图

看看布局、

1、时钟好像来自 J14连接器、而数据来自 J15连接器、时钟和数据是否来自同一个源?

第4层标记为 VCC、是否是电源平面?

3.建议它们为1.1V 和3.3V 创建电源平面、而不是将它们布线为布线

4.建议将电源去耦电容器放置在底层,并在1.1V/3.3V 电源平面和 DP159散热焊盘之间连接电容器。

当问题发生时、它们是否也可以测量时钟输入?

谢谢

David