大家好、

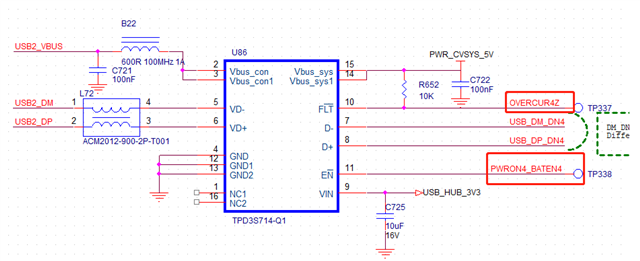

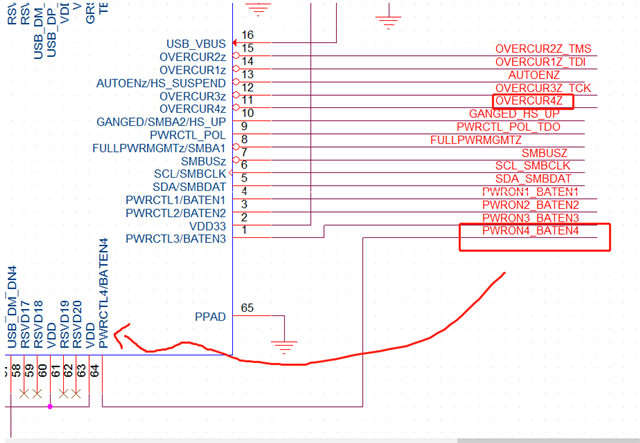

图1中的 USB 保护芯片 TPD3S714-Q1与 TUSB4041搭配使用、其中/FLT 连接到 TUSB4041的 OVERCUR4Z 引脚、EN 引脚连接到 BATEN4、如图2所示。

当前的问题是、在启用 TPD3S714-Q1之前、使用示波器测量/FLT 引脚、显示屏为0V。 在 TUSB4041收集此引脚的状态后、会将其视为故障。

我们怀疑4041被检测为故障状态、并且未启用 TPD3S714-Q1来控制输出、因此无法访问 U 盘。

我们尝试从4041上断开 TPD3S714的10引脚 FLT、发现 U 盘可以正常使用。

芯片应用是否正确? 如何解决此问题?