Other Parts Discussed in Thread: TUSB2046B

您好!

我们遇到了 TUSB2046B 问题。 下面是配置和我们已检查的内容的详细信息。

[配置]

USB2.0全速

Down1、2:未使用

Down3:从未出现问题的 TI (Tiva C) MCU… DFP3

Down4:具有问题…的触摸板控制器(实际上是通用 MCU) DFP4

[调查]

-引脚27:来自振荡器的48MCLK 是稳定的

-复位排序看起来正常。 (集线器 UFP 和 DFP3始终正常)

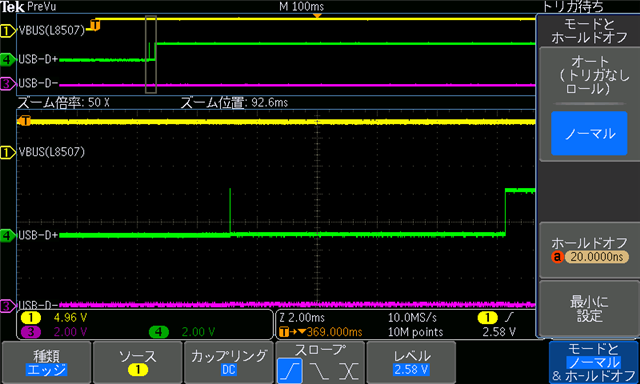

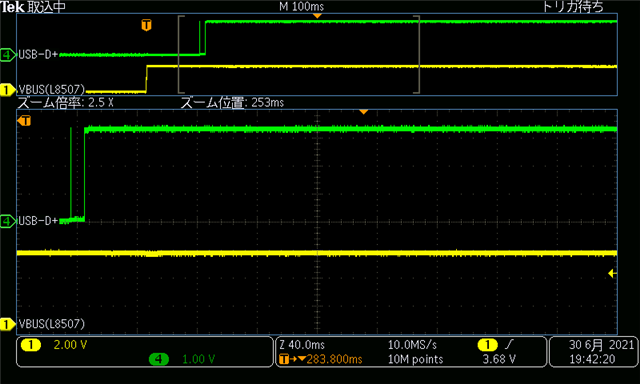

- VBUS 通电大约100ms 后、DFP4会将 D+上拉至高电平。

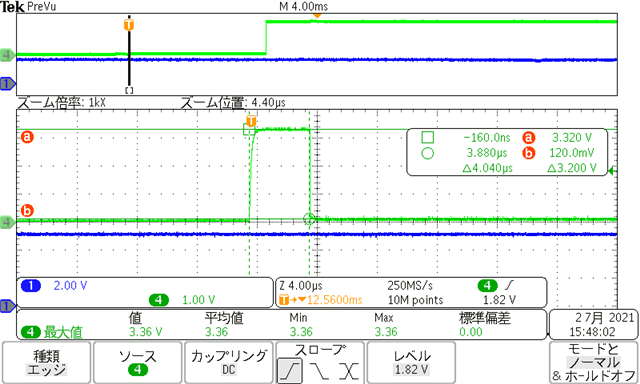

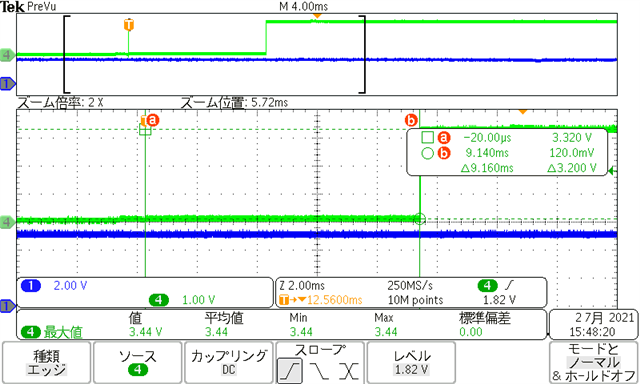

- DFP4器件将 D+切换为(a) 4us 高电平->(b) 9ms 低电平->(c)保持高电平。

这是内部 USB Phy 唤醒时引起的。 这是不可避免的。

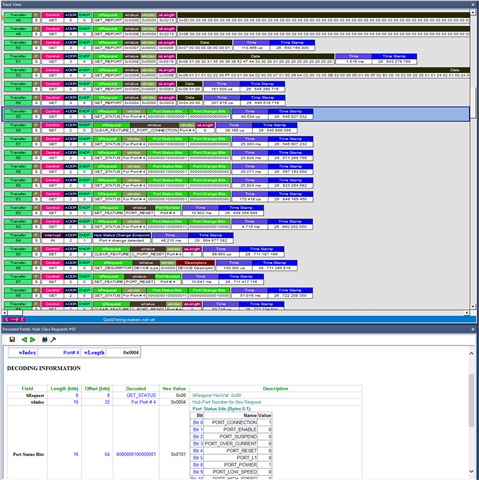

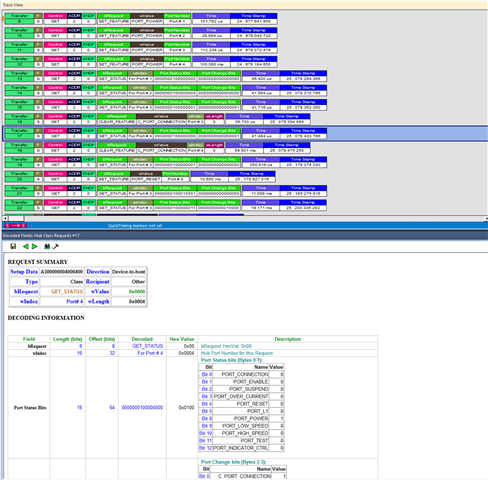

-通过 LeCroy USB 协议分析器,TUSB2046B 未检测到端口4的端口连接。

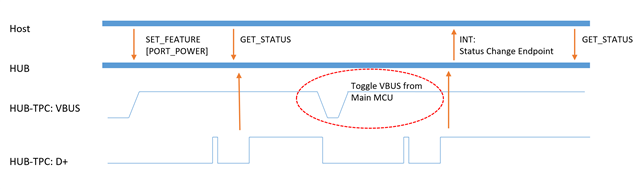

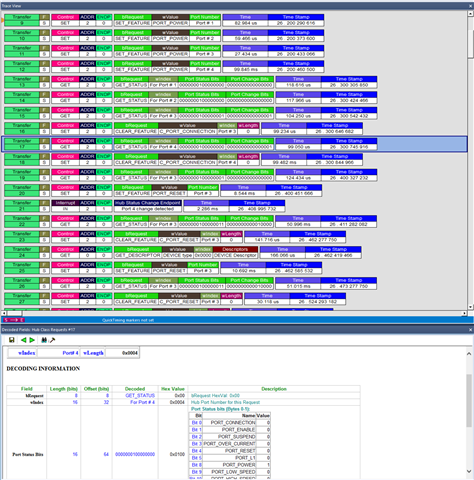

设置 SET_FEATURE (PORT_POWER)后、主机控制器似乎会发出 GET_STATUS 100ms。

DFP4此时可能无法唤醒、但这是可以预料的、因为它需要大约100ms。

我们认为问题是一旦 DFP4处于唤醒状态、TUSB2046B 就不会输出状态更改端点。

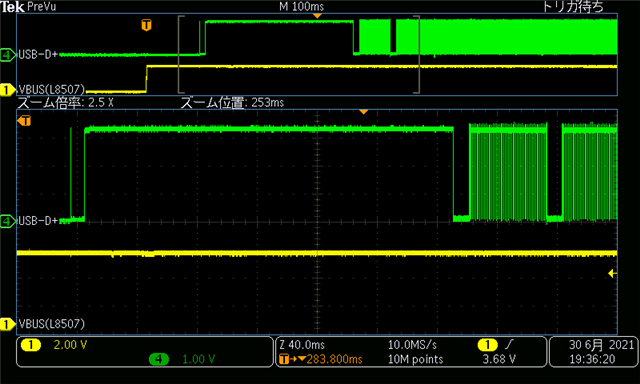

-当问题发生时、我们尝试强制 D+手动拉低、然后释放到高电平。 TUSB2046B 输出状态更改端点并开始通信。

因此,我们假设这一问题是由 TUSB2046B 无法识别 DFP4导致的

问题的几率不是100%。 它似乎取决于触摸控制器 MCU 的 USB 主机控制器、操作系统和硬件型号。

[问题]

我们预计 DFP4设备的行为会以某种方式影响 TUSB2046B 的检测过程。

- TUSB2046B 是否具有4us D+干扰连接/断开检测等极快脉冲?

- TUSB2046B 是否存在 D+低电平超过100ms VBUS 变为高电平的问题?

- TUSB2046在上拉 D+的同时也无法检测下游器件,这有什么原因吗?

- DFP4 VBUS 和 D+:良好外壳

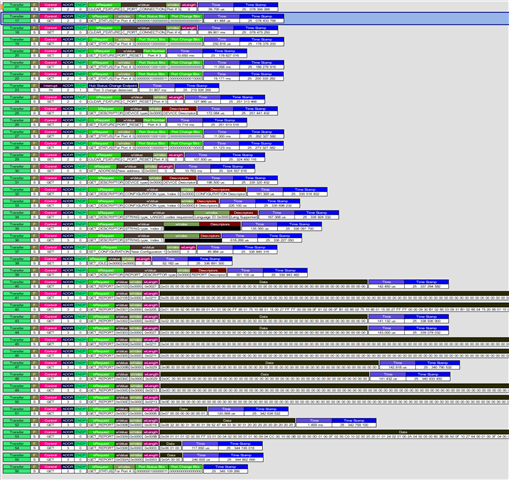

- DFP4 VBUS & D+:故障案例... 无 事务

- 主机和集线器 UFP 之间的日志:良好的情况... 已发布"状态更改端点"

- 主机和集线器 UFP 之间的日志:故障情况... TUSB2046B 从不发出端口4的状态更改

- D+:(A)高脉冲4us

- D+:(b)低9ms