Other Parts Discussed in Thread: SN65HVD234

您好、TI 成员

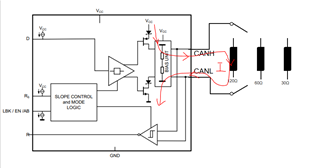

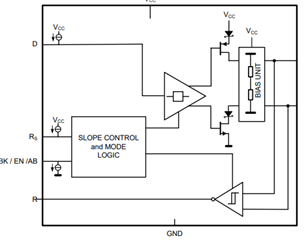

-1:当 D=0或 D=VCC 时,驱动程序如何运行? 它是否通过控制流经 FET 的电流来运行 ?

-当 D=0时,通过 FET 的电流为高电平,当 D=VCC 时,通过 FET 的电流为小电流,对吗?

2:读取 SN65HVD234的数据表;

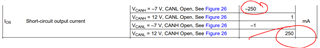

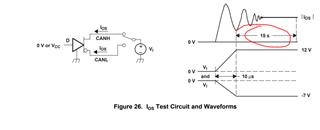

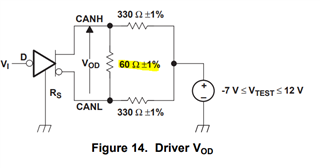

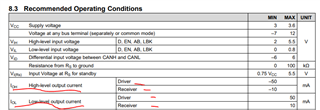

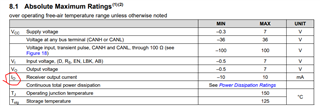

IOH 和 IOL 的参数 ,我无法理解,请

---高电平或低电平是 TXD 信号与其它信号的含义?

电流是 VCC 功耗 还是驱动器功耗?的含义

---为什么电流为50mA, 它是否由 IC 内部控制?

——高电平时 ,为什么输出电流为负(μ A 至50mA)μ A?

3:为什么在此处列出接收器输出电流的 IO,它是一个重要参数吗?

谢谢