你好!

我们将从 MAC 向 PHY 运行 RGMII、10Mbps 模式。

我希望 DP83TD510E PHY 在输入 TX 时钟(TXC)上插入延迟。

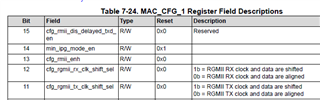

问题1. 我可以看到我们在何处启用延迟插入:

我发现描述文本消歧。 在我看来、文本"1b = RGMII TX 时钟和数据被移位"可以通过两种方式解释:

当 TX 时钟到达 PHY 时、发送器或 PCB 已经延迟了 TX 时钟。

或

TX 时钟由 PHY 延迟。

那么、我们写入"1"还是"0"来在 PHY 中启用 TXC 延迟?

问题2.

如果我们启用 TXC 延迟、会添加多少延迟? 如果可配置、它是哪个寄存器?

问题3.

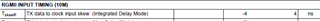

在 DP83TD510E 数据表中、对于10M RGMII 输入、它显示 Tskr=从[-4至4] ns。

这些数字是否假定 PHY 在 TX 时钟上没有插入延迟? 换言之、如果 PHY 设置为插入2ns 延迟、则 TskrR 会增加到[-2至6]ns?

由于数据表中的任何图中都没有显示 TskrR、因此我将对 TskrR 的理解建立在 RGMII 2.0规范的基础上。

(在我看来、我们应该追求一个正最小 Tskr、这样接收到的 TXC 总是在 数据生效后到达... 这可以通过增加 TX 时钟的延迟来实现。。。)