主题中讨论的其他器件:DP83869

您好!

我们在项目中使用的是 DP83869芯片组。 原理图设计已完成。 我们需要对 DP83869电路进行一些回顾。

请进行一些回顾、并向我们提供您宝贵的反馈和任何更正。 请查找随附的 pdf。

请做必要的事。

注意:我们的设计中没有使用任何 MAC,我们需要使用硬件设置选项来控制 PHY 芯片。

谢谢你。

此致、

Sandeep

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Sandeep、

对拖延表示歉意。 我们将能够在本周星期三之前查看原理图并提供反馈。

谢谢、

Nikhil

此通信和任何相关通信中的所有信息均按“原样”和“不含任何瑕疵”提供,并受 TI 的重要声明(http://www.ti.com/corp/docs/legal/important-notice.shtml)约束。

您好、Sandeep、

没问题、感谢您的耐心。

谢谢、

Nikhil

此通信和任何相关通信中的所有信息均按“原样”和“不含任何瑕疵”提供,并受 TI 的重要声明(http://www.ti.com/corp/docs/legal/important-notice.shtml)约束。

您好、Sandeep、

请在下面查找我对所提供原理图的 PHY 部分的评论:

如果您有任何疑问、请告诉我。

谢谢、

Nikhil

此通信和任何相关通信中的所有信息均按“原样”和“不含任何瑕疵”提供,并受 TI 的重要声明(http://www.ti.com/corp/docs/legal/important-notice.shtml)约束。

您好、Nikhil、

对拖延答复表示歉意。 由于工作繁忙、无法回复。

非常感谢您宝贵的评论意见。 我们将采纳您提到的建议。

此时: JTAG: 好的,建议将 JTAG_TDO 拉至低电平以强制执行 OP_Mode 默认设置。

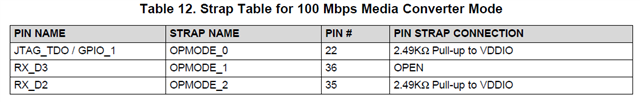

实际上、我们的应用处于100Mbps 媒体转换器模式。 在自举选项表中、它被称为2.49K 欧姆上拉至 VDDIO。 请找到以下屏幕截图供参考。

现在、在我们的原理图中、我们已经使 JTAG_TDO 引脚具有到 VDDIO 的2.49K 上拉电阻。 那么、这是有道理的。

请告诉我您对此的看法。

谢谢你。

此致、

Sandeep

您好、Sandeep、

对这种混乱表示歉意。 建议将 JTAG_TDO 拉为低电平、这是针对默认 RGMII 到铜线配置的。 您的理解是正确的、您可以继续进行上拉。

谢谢、

Nikhil

此通信和任何相关通信中的所有信息均按“原样”和“不含任何瑕疵”提供,并受 TI 的重要声明(http://www.ti.com/corp/docs/legal/important-notice.shtml)约束。