主题中讨论的其他器件:ALP

大家好、

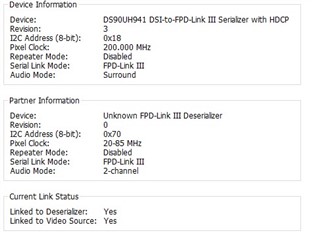

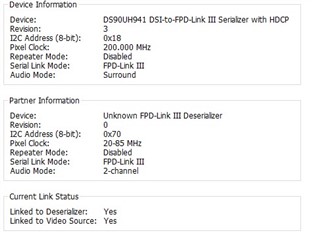

我们的设置是941+984、具有外部双路 DSI 和 CLK。 我们的 DSI 时钟为92MHz*2=184MHz。 但 ALP 显示的是200MHz。 我不确定这是否是偏差? 此外、您能否帮助检查941的寄存器设置? 非常感谢、

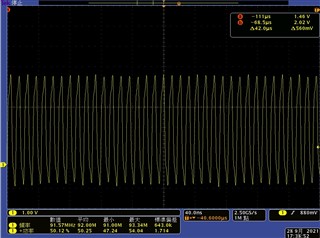

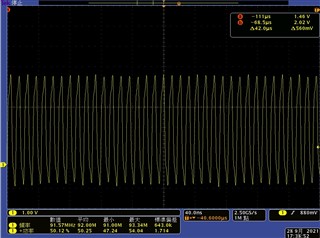

(DSI 双端口、DSI CLK0和 DSI CLK1 为92MHz、如下所示)

e2e.ti.com/.../auo-dsi-display.nrd

此致、

罗伊

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们的设置是941+984、具有外部双路 DSI 和 CLK。 我们的 DSI 时钟为92MHz*2=184MHz。 但 ALP 显示的是200MHz。 我不确定这是否是偏差? 此外、您能否帮助检查941的寄存器设置? 非常感谢、

(DSI 双端口、DSI CLK0和 DSI CLK1 为92MHz、如下所示)

e2e.ti.com/.../auo-dsi-display.nrd

此致、

罗伊

您好、Michael、

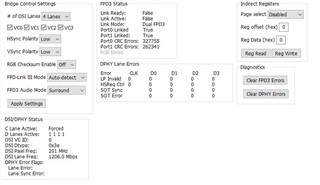

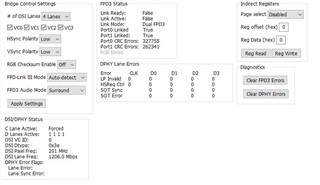

上述问题已得到解决。 现在我们面临另一个问题。 现在、我们使用外部 DSI 来启动显示屏、但我们发现941 <->984之间的链路将丢失。

链路就绪有时为 True、有时为 False、但大多数时间为 False。 您能告诉我可能的根本原因吗? 或我们忘记设置的任何寄存器?

我们使用了941 internal Patgen 来成功显示。 链路稳定。

此致、

罗伊

您好、Michael、

有关941寄存器内容、请参阅此文档。 很难获得链路稳定寄存器、因为链路稳定< 1s

[引用 userid="424310" URL"~/support/interface-group/interface/f/interface-forum/1040050/ds90uh941as-q1-dsi-clk-difference-info-in-alp ]AUO DSI display.NRD[/quot]罗伊

您好、Michael、

它们使用信号发生器来生成所需的 DSI 信号。 他们已经验证了另一个项目中的信号是否正常。 下面是我们使用外部 DSI 和941内部 Patgen 时的寄存器转储。 根据已讨论、在外部 DSI 模式下、FPD 链接状态为 False。 此外、984上的 LOCK 引脚也处于低电平。

e2e.ti.com/.../auo-dsi-display.zip

e2e.ti.com/.../auo-pattern-generator-display.zip

此致。

罗伊