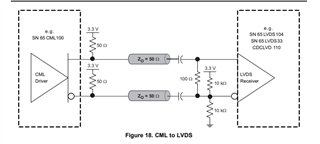

大家好、我将 DS90LV012A 用作 CML 接收器。 我的输入当前是交流耦合的、输入之间的阻抗为100欧姆 R。 我是否需要在输入侧提供任何其他偏置? 有关该器件的另一个主题引用 了 https://www.ti.com/lit/an/scaa059c/scaa059c.pdf 并提到了图18和19。 两者都是交流耦合 CML 至 LVDS、但图18用于内部自偏置、图19假设存在内部生成的偏置电压引脚(VBB)。 DS90LV012A 没有 VBB 引脚。

1.既然 TI 参考了本文档、那么可以放心地假定该器件是自偏置的、并且不需要外部偏置来创建共模吗?

2.图18第11页中的3V3 10k 分频器是否存在、以确保在未连接驱动器时输入不会悬空? 这些是必要的吗?

DS90LV012A DS 中有关 VCM 和 VID 电气参数的注释、注释3难以理解可接受的范围。 它提到: 。 当 VDD = 2.7V 时、VCM = 0.05V 至2.35V 或当 VDD =|VID|/2至 VDD−0.3V 时、VID 不允许大于100mV

在我看来、如果 VDD = 2.7V 或3.3V 时 VCM < 50mV、VID 只能高于100mV ...

但随后、它们显示了 VCM = 1.2V 和200mV VID 的测试模式... 我知道 LVDS 规格是100mV 到600mV VID,1.2V VCM,所以我缺少什么:) ?

谢谢、

Adam