请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPD12S016 您好!

关于 TPD12S016上的外部上拉、我的客户提出了一个问题。

(问题)

此器件是否在 A-Port 支持外部上拉?

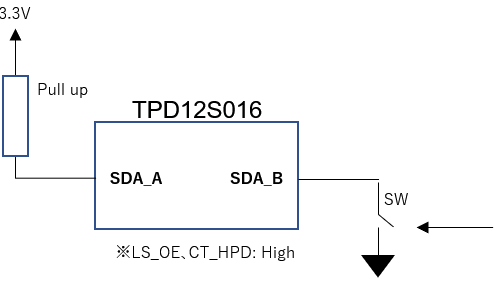

他们通过以下测试进行了确认,但 A-Port 输出不满足低电平要求

(结果)

上拉电压:3.3V,B 端口输入:低电平

・A 端口输出:2.16V @上拉电阻=1k Ω

灌电流:()3.3-2.16 μ A/0.9k=1.254mA

・A 端口输出:0.84V @上拉电阻=10K Ω

灌电流:()3.3-0.84 μ A/5k=0.432mA

我从数据表第17页(如下所示)了解0.4V 输出时的灌电流为3mA。

我想知道为什么驱动电流很低。

“在0.4V 电压下能够灌入3mA 电流的 CMOS/NMOS 开漏将具有133 Ω 或更低的输出电阻(R = E/I)。”

如果该器件不支持外部上拉、您是否有支持 DDC 线路上电平转换器的外部上拉的器件?

或者您是否有其他解决方案?

此致、

TAO_2199