大家好、

这是 Brandon、客户、我在使用 ds110df111时遇到了一些问题:

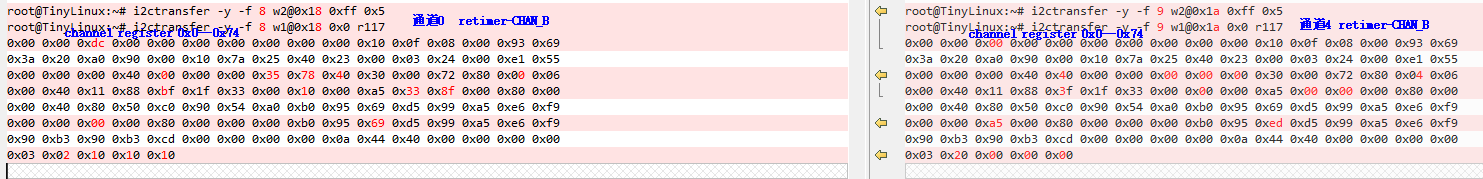

- 其中一个输入源是 Intel XL710 NIC、具有10G SFI.0x51信号衰减为0、输出到 XFI。 其他通道输入源为10G XFI、信号衰减为1、输出到 XL710 NIC 上的 SFI。 目前、两个通道都处于下行链路状态。 此问题的根本原因可能是什么、应设置任何特殊配置?

- DS110DF111配置为通过将 CHAN_REG 设置为0x54来循环。 IN 信号是否作为原始信号发回? 还是在重定时器上进行内部 CDR 处理之后? 重定时器配置是否对其回送功能有任何影响

BR

Brandon