你(们)好

我们使用 SN65DSI83将 DSI 转换为 LVDS。 我们的处理器只有两个 DSI 对、IO 电压为3V3。

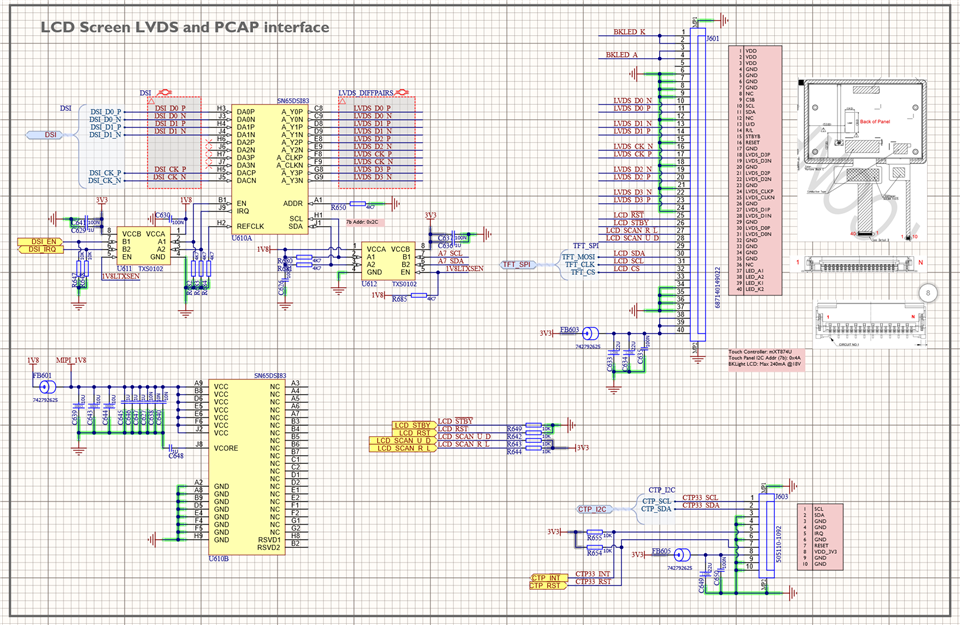

我想知道您能否为我们查看原理图? 请参阅随附的图像

提前非常感谢您

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Navin、

您是否已检查此器件的吞吐量是否足以仅支持2个 DSI 数据通道? 请参阅此常见问题解答: https://e2e.ti.com/support/interface/f/interface-forum/945185/faq-sn65dsi84-sn65dsi83-sn65dsi84-and-sn65dsi85-resolution-guide

我还建议为外部 REFCLK 添加一个用于调试的位置(您只需将其保留在 BOM 中)。

此致、

I.K.

你(们)好,IK

抱歉、在我完成上一个帖子之前按了发送、

我想知道上述计算是否正确? 我的 LVDS 屏幕最大时钟频率为50MHz、目前我们使用的是16bpp。

对于调试外部 REFCLK、我是否可以使用与 EVK 中所示完全相同的 CDCEL913PW?

否则、电路的其余部分是否正常?

提前感谢

Navin