TCA9617A 的拉伸和仲裁机制是如何工作的?

在序列(1)处有多少延迟时间?

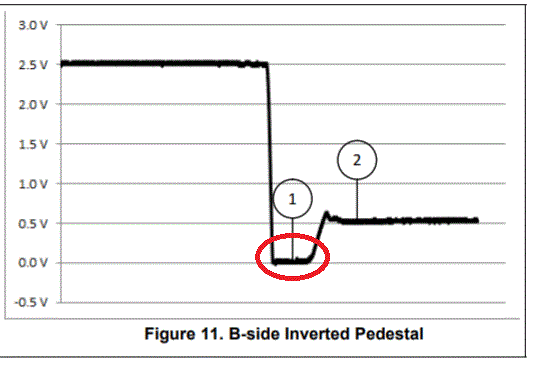

为什么 B 侧有0.5V 的失调电压?

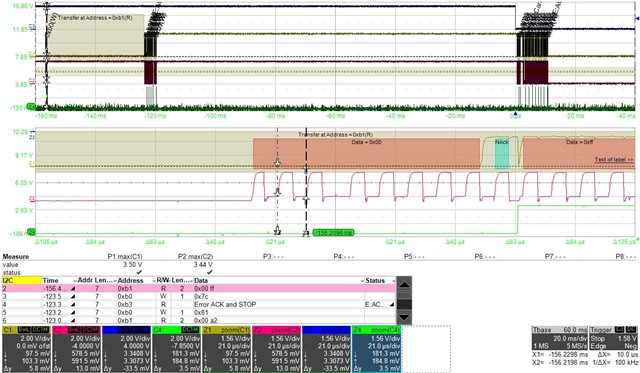

如果序列(2)存在信号干扰、将压降设为0V、然后恢复至0.5V、此时一端会产生什么影响?

我们发现、当信号在序列(2)处受到干扰时、我们将丢失 A 侧时钟。 波形如下面所示。

BR、

Gary

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您是指时钟拉伸? 器件本身只会将低电平从一侧复制到另一侧(无论哪一侧)。 它不会使不支持时钟扩展的 I2C 器件成为支持时钟扩展的器件、而只是允许执行时钟扩展的 I2C 器件通过驱动低电平来执行该操作。

仲裁也是如此、器件本身不执行器件仲裁。 它只是将一个低电平从任一侧重新驱动到另一侧。 从技术上讲、该器件会引入传播延迟、从而使仲裁更加困难。

我认为我们在技术上没有该规格、但我认为它具有从高单个数字纳秒到低两个数字纳秒的范围。

[引用 userid="205271" URL"~/support/interface/f/interface-forum/985508/tca9617a-tca9617a-a-side-clock-loss-question "]并且为什么 B 侧有0.5V 的失调电压?[/quot]该器件支持双向信号、为此、我们需要能够防止其自身的输入看到其输出。 (器件的输入和输出直接连接到自身)。 问问自己、如果我输出一个低电平、而我自己的输入看到一个低电平并尝试向另一侧输出一个低电平、会发生什么情况? 它会一直保持低电平。 500mV 失调电压修复了以下问题:由于输入只识别低于400mV 的逻辑低电平。 因此、如果 A 侧看到低电平、B 侧将驱动低电平、但其自身的输出低电平(在 B 侧)将不会被其自身的输入(B 侧)看到、从而防止了我之前描述的一直处于低电平的困境。

在此处进一步阅读:

https://www.ti.com/lit/an/scpa054/scpa054.pdf

如果按顺序(2)驱动低于0.4V 的电压、则一侧的 TCA9617的低侧驱动器将驱动为低电平。 一旦恢复到0.5V、低侧驱动器将释放、但如果您处于序列(2)、则从技术上讲、一侧应该仍然为低电平。 (当一个侧被从外部驱动为低电平时、序列2发生)。

发生这种情况时、SCLA 和 SCLB 的两侧是否可以处于相同的范围内?

-Bobby