主题中讨论的其他器件:AM3352、

您好!

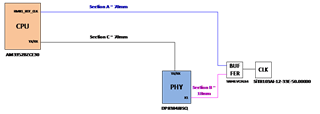

我们将 AM3352和 DP83848JSQ/NOPB 用于以太网服务接口。

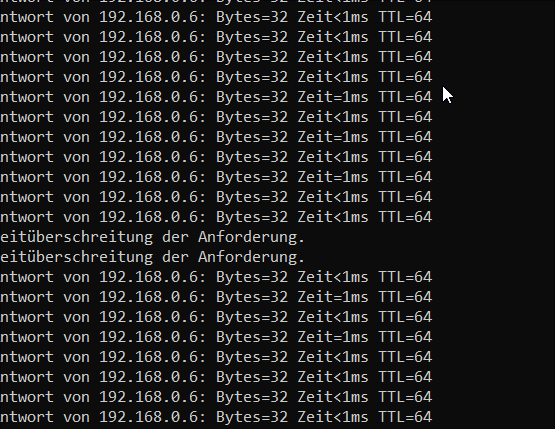

我们在这里看到以太网连接在一段时间内中断一次:

ping 和建立连接都不起作用,或者一切都正常,而且突然中断。

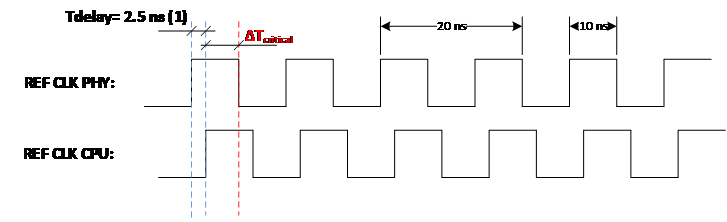

我们在开发过程中遇到了一些 EMC 问题、并针对 ETH PHY 提供了 REF:CLK 的一些权变措施。 此外、时钟源与 Sitara 之间的距离很远。 我们还知道、采用 SN74LVC2G14DCK 缓冲器的解决方案并不是最佳解决方案。 一种权变措施是将 C517增加到33pF、以减少到 Sitara 的延迟。

这样、我们将 U500引脚28 (DP83848JSQ/NOPB)和 U100引脚 K18 (AM3352BZCE30)之间的延迟从2、65ns 降低到~ 2ns。

PHY 标记:

2021:

88A80R63

83848JSQ

2016年:

49ANJKG3

83848JSQ

除了延迟之外、还有什么其他事情可以在这里发挥作用? 还是只需要将延迟保持在2ns 以下? 请找到所附的原理图和布局。

期待您的回答。

e2e.ti.com/.../2870.Mainboard_5F00_CPU_5F00_ETH_5F00_PHY.pdf

此致、

阿伦