请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TS3DV642 您好,

这是我之前的论坛帖子的后续问题

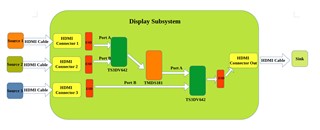

我们已成功完成了原理图设计、如博文中提到的解决方案2所示

对于布局限制、我几乎没有疑问。

–TSDV642数据表中最小的 R ON 如下所示

–端口 A:6.5 Ω

–端口 B:8.2 Ω

差分对的 HDMI 2.0阻抗如下所示

- 每个 TMDS 信号的单端阻抗应为50 Ω±10%。

- 每个 TMDS 对的差分阻抗应为100 Ω±5%。

那么我的问题是,我应该降低电容端口(A 和 B)上指定阻抗的 R ON 电阻吗?

如果是、那么单端和差分阻抗的相关性是多少?

此致

Sreekanth MK