Other Parts Discussed in Thread: SN65DSI83

主题中讨论的其他器件: DSI 调谐器

您好!

我目前正在使用 SN65DSI83的评估板。

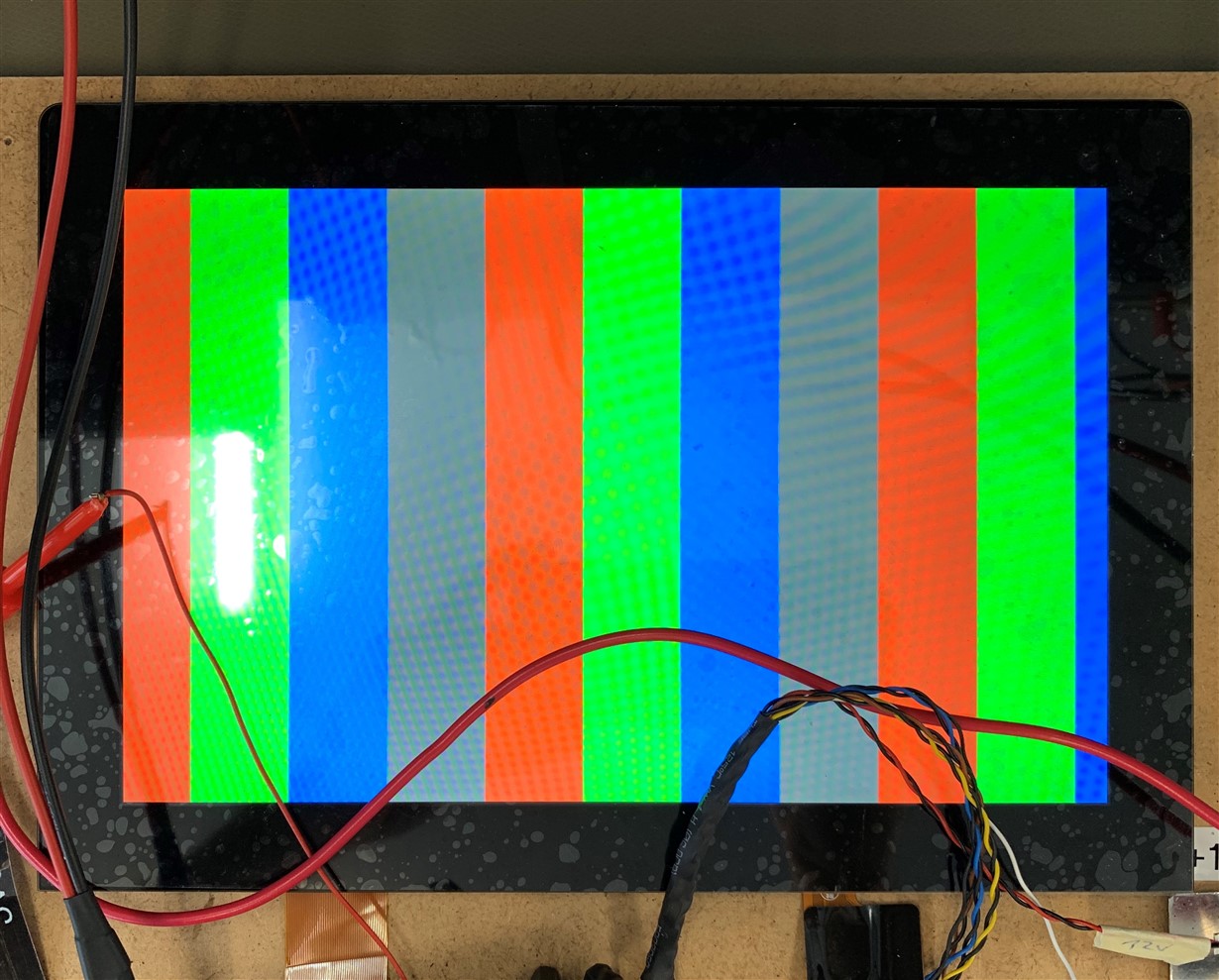

首先、我想在显示屏上显示测试图案(AUO B101EAN01.2)。

我想将27MHz LVDS_REFCLK 用于 LVDS 时钟。

(从 Y1中检查了 R33的频率)

如果我在通道 A 的 J6上检查 LVDS 信号、我会正确测量数据信号、但我不会在 FlatChA_CLKP 和 FlatChA_CLKN 上测量信号。

对于 DSI 调谐器、我选择了以下设置。

如果有人能帮我、我会很高兴。

谢谢