编辑:忽略此内容并转至我在下面撰写的下一篇文章。 我在这里不正确地理解了这个问题。

我有一位客户使用 XIO2001在原型板上工作-他们正在进行调试。

该器件的大多数功能似乎都能正常运行。

但是、当它们确认了奇偶校验警报尝试和启动时的行为时、XIO2001寄存器显示奇偶校验错误、但 PERR 引脚不会被驱动为低电平。 它保持在 Hi-Z 状态

在此类错误期间、将 PERR 驱动为低电平的正确设置是什么?

这些是从 CPU (PCIe)端看到的寄存器设置。

70800000:104C 8240 0007 0010 0000 0604 0000 0001 .L@……

70800010:0000 0000 0000 0000 0000 0000 0000 0101 02A0 …

70800020:0000 0000 0001 0000 0000 0000 0000 0000 0000 0000…

70800030:0000 0000 0040 0000 0000 0000 00FF 0001 … @………

70800040:480D 0000 0000 00005001 0603 0008 0040 H.… 第...页。 @μ A

70800050:7005 0088 0000 0000 0000 0000 0000 0000 0000 p...........

70800060:0000 0000 0000 0000 0000 0000 0000 0000 0000 …

70800070:0010 0072 8002 0000 2000 0010 4C11 0006 ... r... ...等等...

70800080:0000 1011 0000 0000 0000 0000 0000 0000 0000…

70800090:0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 …

708000A0:0000 0000 0000 0000 0000 0000 0000 0000 0000 …

708000B0:0000 0900 0000 001F 0000 0000 0000 0000 0000 0000 …

708000C0:0001 0208 0108 0012 2000 3214 0000 0000 … 2…

708000D0:0000 0000 025F 8600 0000 0040 0000 … _。。。 @……

708000E0:0000 0000 0000 0443 0008 007F 01C0.......... C.

708000F0:0000 0000 0000 0000 0000 0000 0000 0000 0000 …

70800100:0001 0000 0000 0000 0000 0000 2031 0006 ........ 1.

70800110:0000 0000 2000 0000 00A0 0000 0000 0000 0000… 三

70800120:0000 0000 0000 0000 0000 0000 0000 0000 0000 …

70800130:17A8 0000 1340 0000 0000 0000 0000 0000 … @………

70800140:0000 0000 0000 0000 0000 0000 0000 0000 0000 …

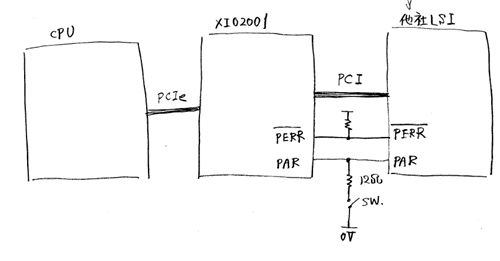

这是他们采用的方法:

-设置 PCI 总线周期的数据阶段,以便可以将参数=H 的数据写入 LSI (XIO2001的 PCI 端)

- CPU 以长(32位)数据为引线,以便 PCI 总线周期的地址阶段为 PAR = L

-在 CPU 领先的情况下、一个开关通过12Ω Ω 电阻器将 PAR 引脚(连接到 XIO2001和 LSI)连接至0V -强制出现奇偶校验错误

-寄存器1E 变为83A0、但 PERR 信号保持高阻态

进行确认

-他们用数据编写 LSI,使 PAR = L,然后对交换机执行与上述相同的设置。 1E 寄存器区域变为02A0、PERR 保持高阻态 这是预期行为。