Other Parts Discussed in Thread: DP83822I

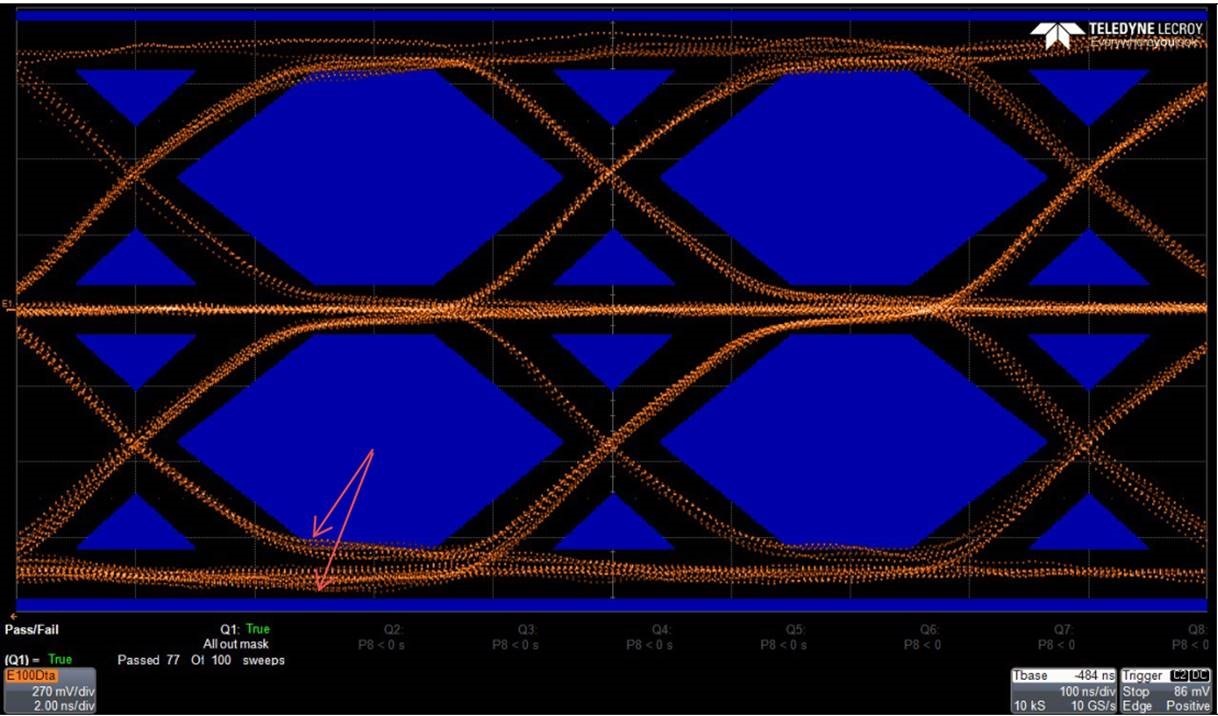

继续讨论以下主题: DP83822I 眼图测试故障(双绞线有源输出接口模板): https://e2e.ti.com/support/interface/f/138/p/934624/3456264#3456264

我们尝试短接 L800、但仍然失败;

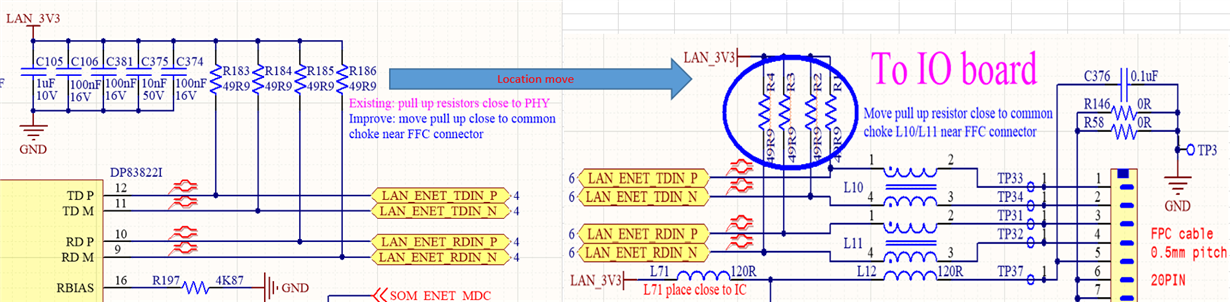

我们还优化了 PCB 和 FPC 布局、但仍然失败、请。 参考 附加的测试报告。

一个问题、是什么参数导致了此故障? 信号噪声、上升/下降时间或其他参数? 我们可以修改49.9欧姆上拉电阻来改进它吗?

BTW:我们使用另一个解决方案/IC 设计了类似的 PHY 电路、即使使用更长的 FPC 和 PCB 布线、但始终获得通过结果;