请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DS92LV2421 主题中讨论的其他器件:LV24EVK01

您好、专业人士、

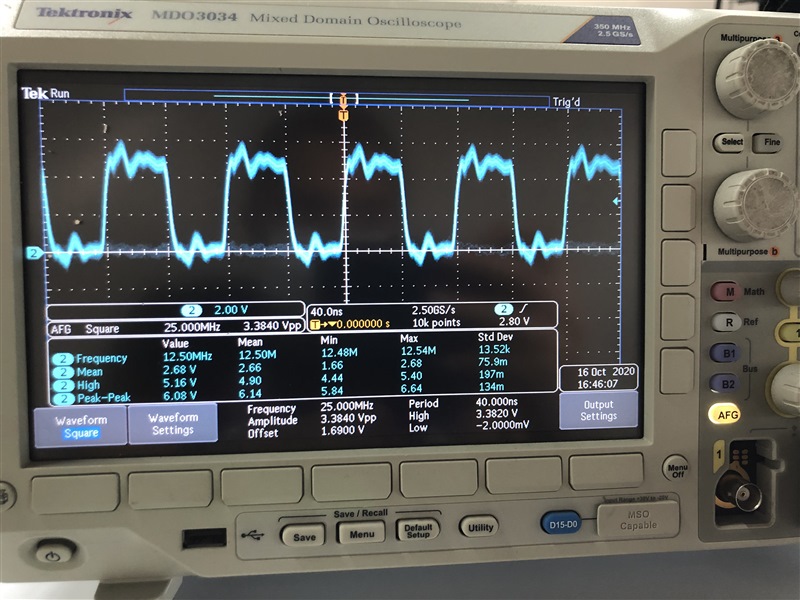

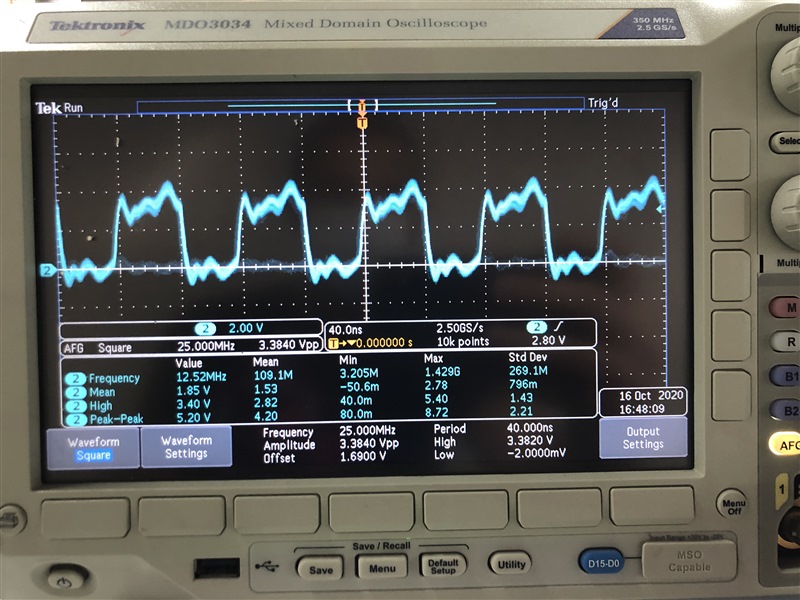

我目前正在尝试在特定视频面板应用中使用解串器/解串器(LV24EVK01)实现。我从 FPGA 提供串行器的输入时钟(25MHz)信号。 但解串器的 LOCK 和 PASS 引脚不会变为高电平。 它不能与下方发布的信号配合使用。 我尝试提供一些其他信号作为其他信号源的时钟源、它们工作良好。 我对 ser/DES 对的输入引脚接受的最大值为3.3V、一些其他示波器生成的5V 10MHz 时钟信号也起作用。 我正在上传从 FPGA 生成的2个信号、其中一个为5V、另一个为3.3V。 你能告诉我,在我的发言中可能会有什么问题吗?