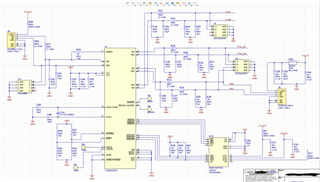

随附的是我在新设计中放置的原理图。

R49为 DNP

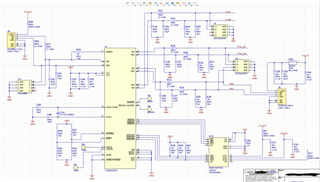

将 USB 电缆连接到 J4后、我无法读取 USB 端口上的任何内容。

大多数情况下、我没有看到任何设备插入到计算机中。

检查 U9.P9、P13、P17后、所有引脚被拉高。

U9.P10、P14、P18也有助于提高。

由于 PWRON1未变为低电平、因此数据不会传递。

您能否告诉我需要进行哪些更改、以便 U9将 PWR 引脚拉至低电平?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

随附的是我在新设计中放置的原理图。

R49为 DNP

将 USB 电缆连接到 J4后、我无法读取 USB 端口上的任何内容。

大多数情况下、我没有看到任何设备插入到计算机中。

检查 U9.P9、P13、P17后、所有引脚被拉高。

U9.P10、P14、P18也有助于提高。

由于 PWRON1未变为低电平、因此数据不会传递。

您能否告诉我需要进行哪些更改、以便 U9将 PWR 引脚拉至低电平?

您好!

这是自供电还是总线供电设计? BUSPWR 连接到测试点、需要根据设计是总线供电还是自供电设计将其上拉至高电平或低电平。

您还需要在 RESET 引脚上创建 RC 复位电路。 我会将 R42更改为1uF 电容器。 您 μs 确保在3.3V VCC 达到90%后、脉宽在100 μ s 至1ms 之间进行复位。 您还 μs 确保时钟信号必须在复位窗口的最后60 μ s 内有效。

谢谢

David