请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TUSB522P 大家好、我将为我的 USB 系统使用 TUSB522p。

我有一个简单的问题。

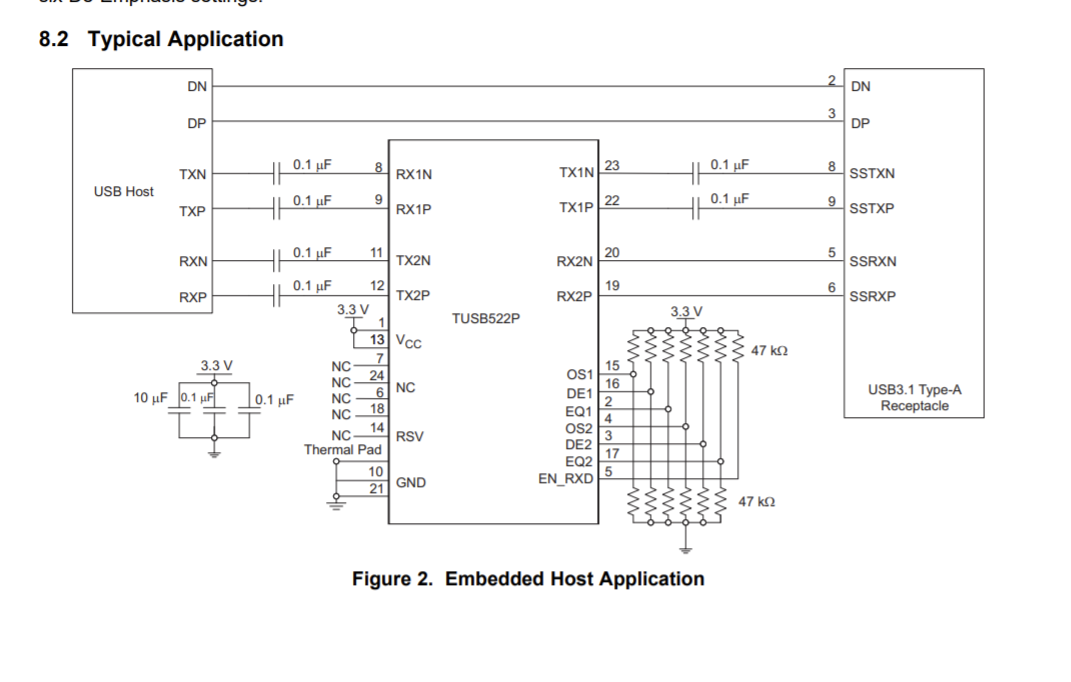

在下面的典型应用中、

OS1和 OS2引脚均为上拉电阻、下拉电阻为47k Ω。

我知道 EQ 和 DE 引脚具有中电平输入、但 OS1和 OS2引脚仅具有高电平或低电平 CMOS 输入。

如果我像典型应用那样设置上拉和下拉、则 OS1和 OS2将具有什么逻辑值?

谢谢。