Other Parts Discussed in Thread: TLK1221

您好!

使用 TLK1221时、我有疑问。

引脚配置如下所示:

我的测试程序:每1ms 发送一组数据、即 AABBCCDD+COUNT、COUNT 是一个从0到255的计数器值、并在空闲时发送 x"BC"(K28.5)。

发送数据时、我使用 PrSL_REFCLK_s;接收数据时、我使用 TLK_RBC0。

1) 1)当我启用循环功能、从而使 TLK_LOOPN <="1"时 、接收到的数据是正确的。

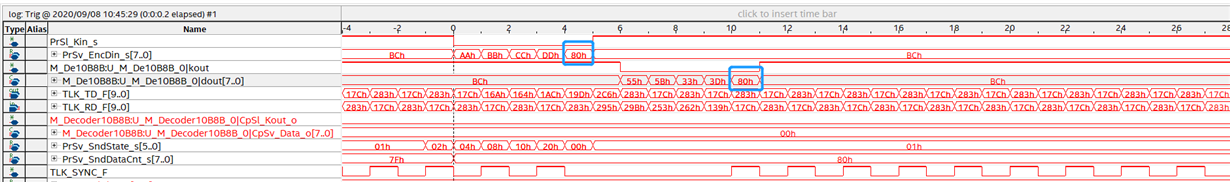

PrSv_EncDIN_s 是要发送的数据、TLK_TD_F 是发送到 TLK1221的8b/10b 编码数据;TLK_RD_F 是发送到 FPGA 的 TLK1221的接收数据、DOUT 是解码数据。 下图显示了发送和接收是一致的。

SignalTap 的采样时钟是 TLK 的输出时钟 RBC0。

2) 2) 使用 SATA 电缆连接 J3/J4、蓝色表示计数值、有时是正确的、有时是错误的。 接收到的前4个数据固定为555B333D。

使用一张卡进行发送和另一张卡进行接收时,问题仍然存在。

3) 3)原理图如下、请帮助分析、谢谢!