https://e2e.ti.com/support/interface-group/interface/f/interface-forum/914208/tusb542-tusb542rwqr

器件型号:TUSB542降级器、

早上好。

我对使用 TI 转接驱动器 IBIS (TUSB542RWQR)模拟 ADS 有疑问。

我不知道您对 DE 和 EQ 的描述是什么。 请帮我这个忙、非常感谢。

问题1:

如果 ADS 的 EQ 和 DE 设置如下所示:(我们的 Pass 设置)

Tx1/TX2:EQ:0 (TI IBIS 用户指南为0dB);DE:3 (OS:1100mV、DE:TI IBIS 用户指南为0dB)

RX1/Rx2:eq:0 (TI IBIS 用户指南为0dB);de:3 (OS:1100mV、DE:TI IBIS 用户指南为0dB)

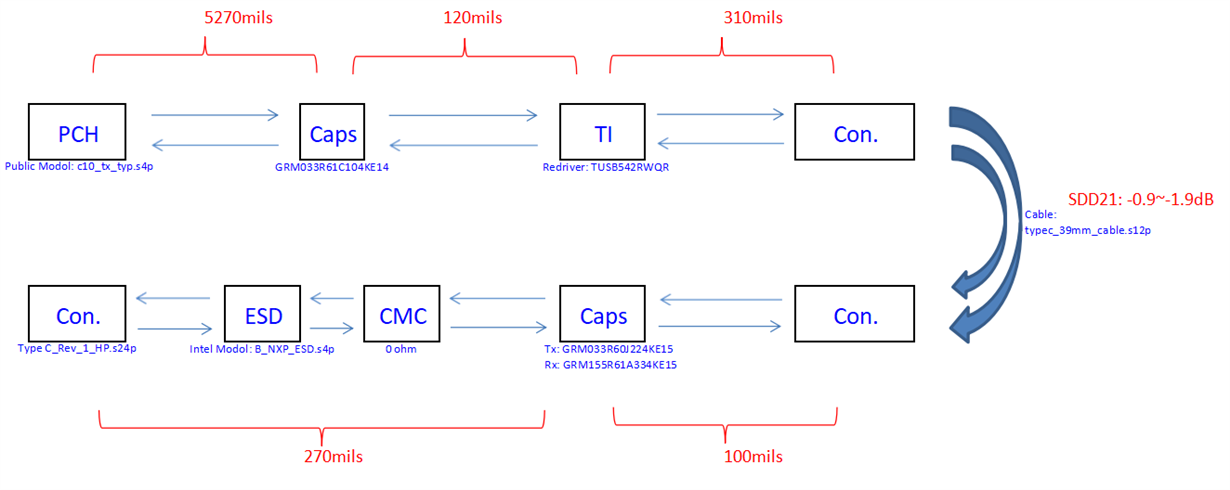

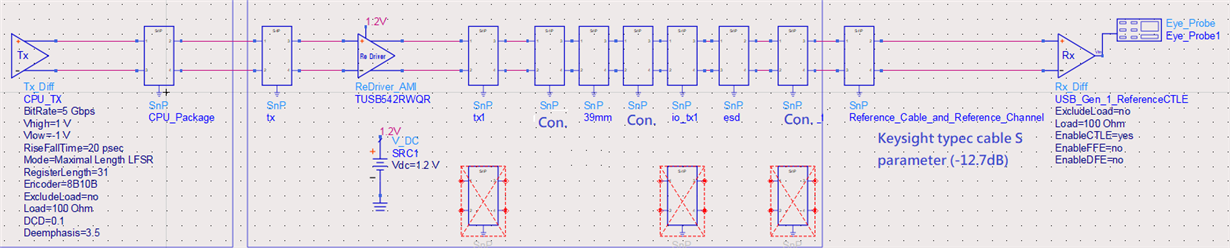

根据上述问题...如何设计我们的 DUT 硬件设置?

PS:硬件设置定义为第13页的表2、请参阅 TUSB542 SLLSER3E–2015年12月–2017年6月修订版。

非常感谢。