Other Parts Discussed in Thread: DS92LV18

您好!

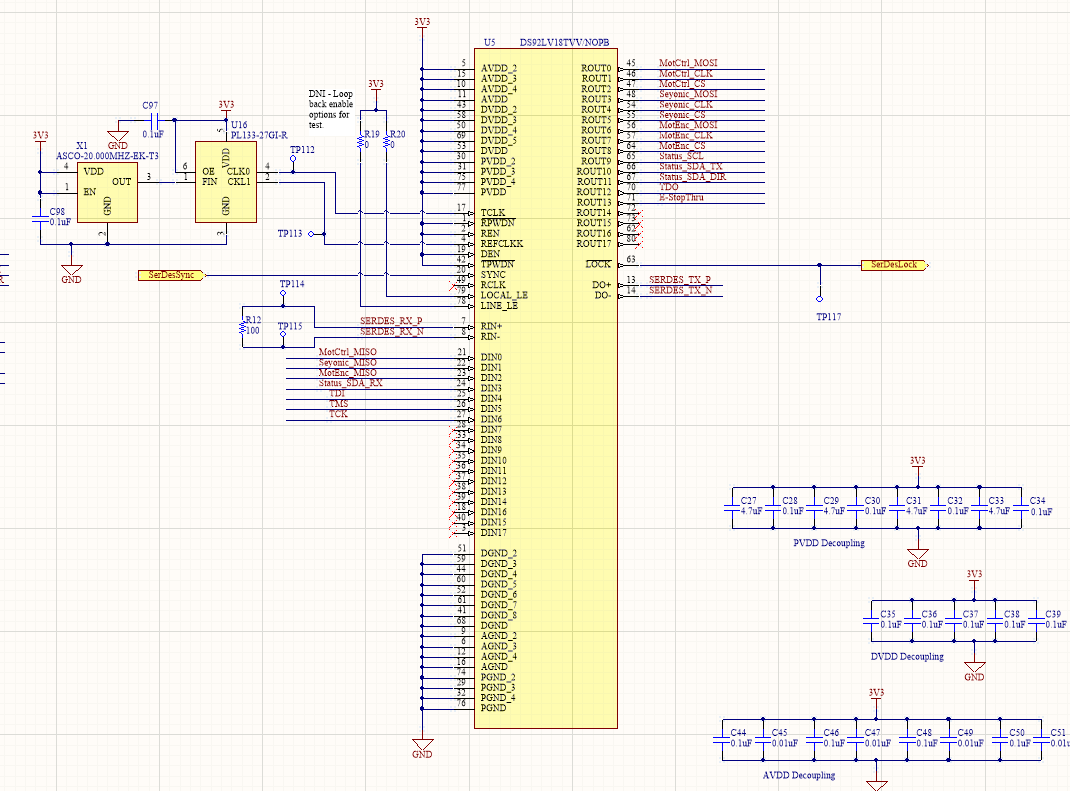

我们在 uC 和 FPGA 之间使用 DS92LV18。 我注意到、当我在 uC 上遇到断点并且串行传输停止时、同步会丢失、并且我必须将 Sync 位置为有效一两秒才能使其恢复同步。 没有问题、这是预期的。 但是、它提出了一个基本问题-我需要在一对 SerDes 器件之间传输消息的频率如何、以确保嵌入式同步符号保持同步? 启动时、我会在尝试交换消息之前发送同步模式、但如果消息流量本身能够保持链路的完整性、我宁愿避免再次发送同步模式。

谢谢、

Jamie