请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TS3DV642 大家好、

我的客户使用 TS3DV642进行设计、以便在 LVDS 和 eDP 之间切换、操作正常。

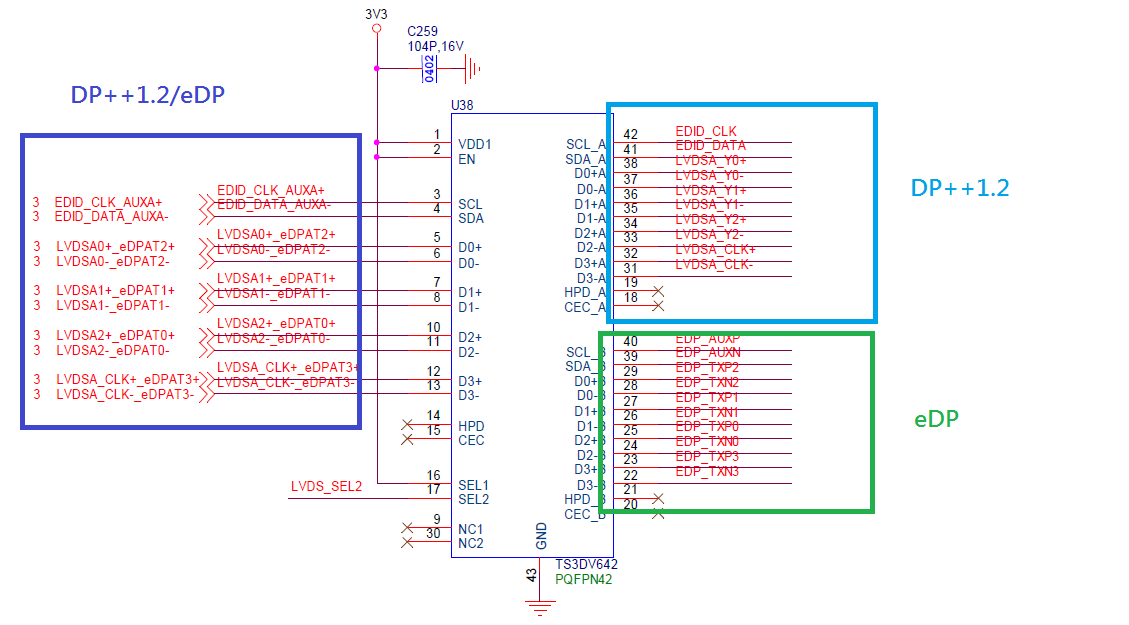

现在、他们想要扩展应用、以便在 DP++1.2和 eDP 之间切换、如下所示。 请您评论一下 TS3DV642是否适合此应用? 谢谢!

适用于 DP++1.2和 eDP 的新型多路复用器设计:

DP++1.2/ eDP 输入:

此致、

Sam Ting