您好!

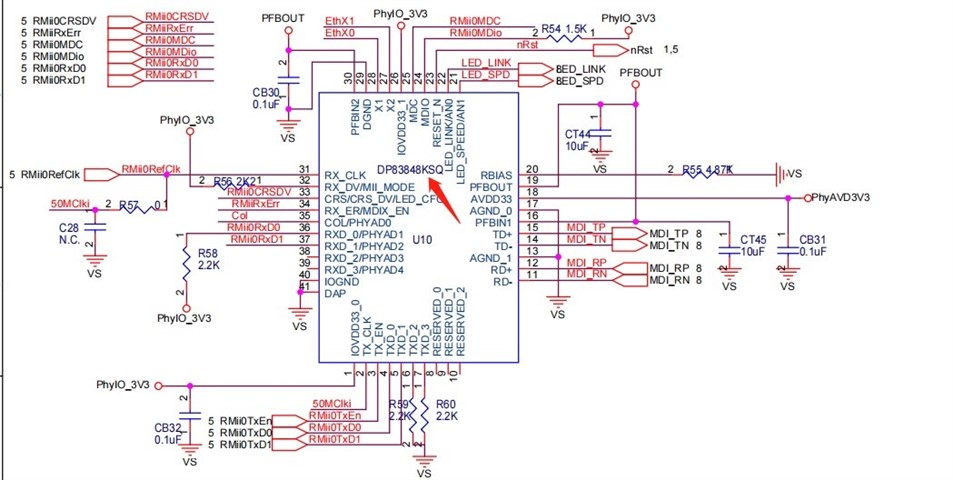

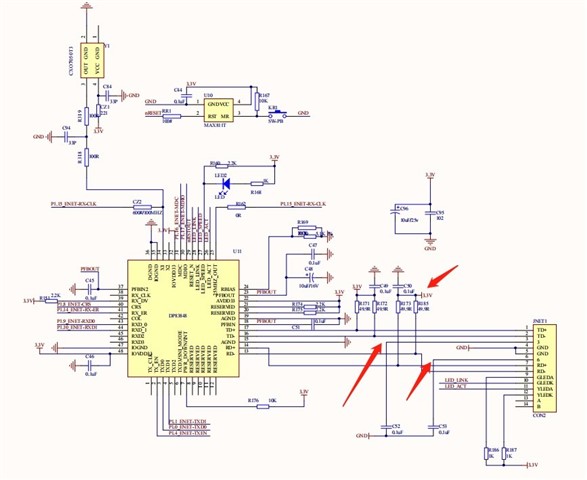

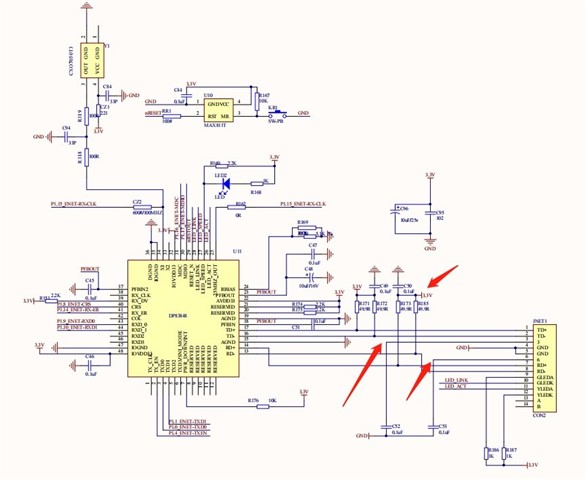

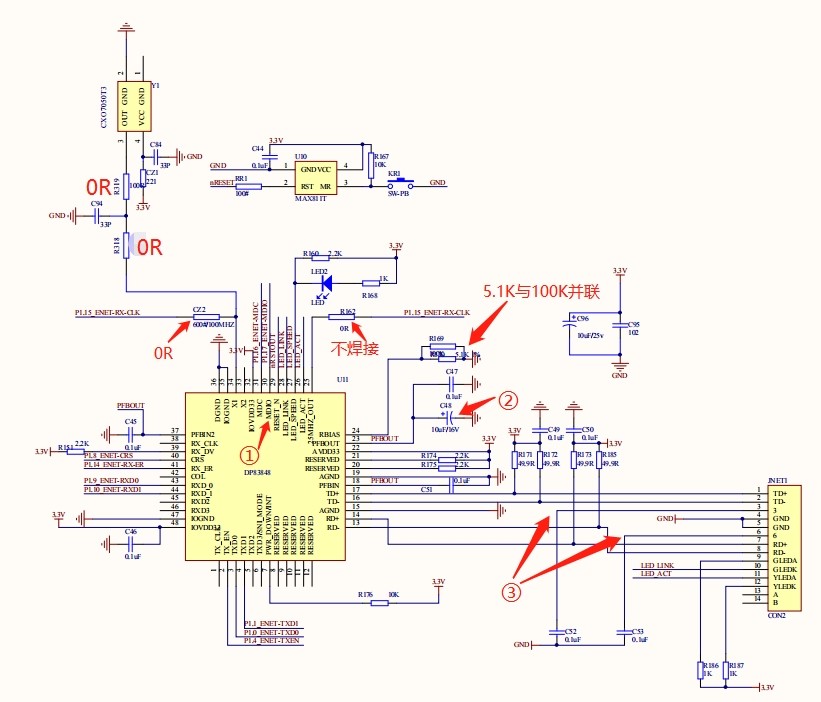

上图是这个 PHY 芯片的原理设计。 中文字符和参数是 PCB 板的实际焊接值。

标签①MDIO 引脚未与1.5K 上拉电阻器连接

标签②带极性电容器的10uF 此处是实际焊接的10uF/25V 直列式电解电容器

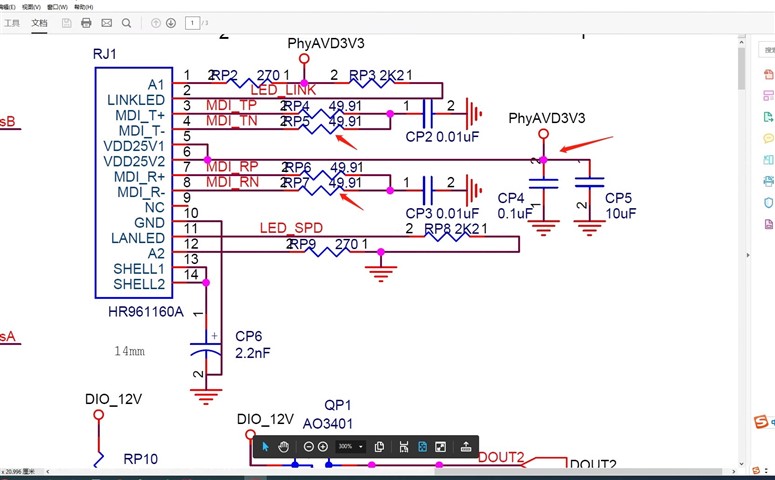

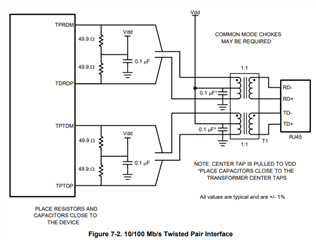

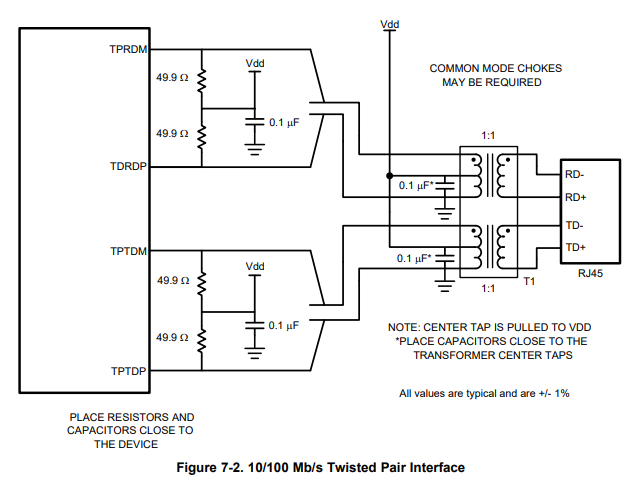

变压器的中心抽头是否需要在此处连接到3.3V 电源?

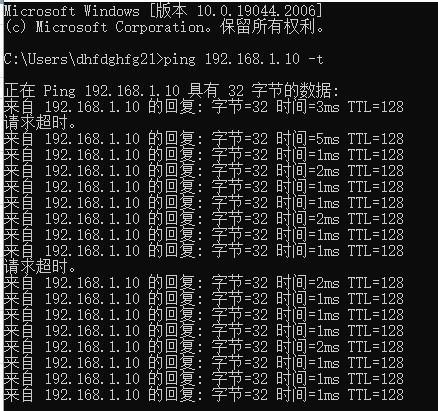

然后、在 ping 网络端口的 IP 地址上发现丢包和发送延迟。 上述综合原理图设计(①、②、③)是否会影响数据包丢失和延迟? 在原理图中、C94未焊接在 PCB 板上。

2.

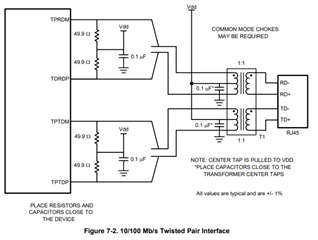

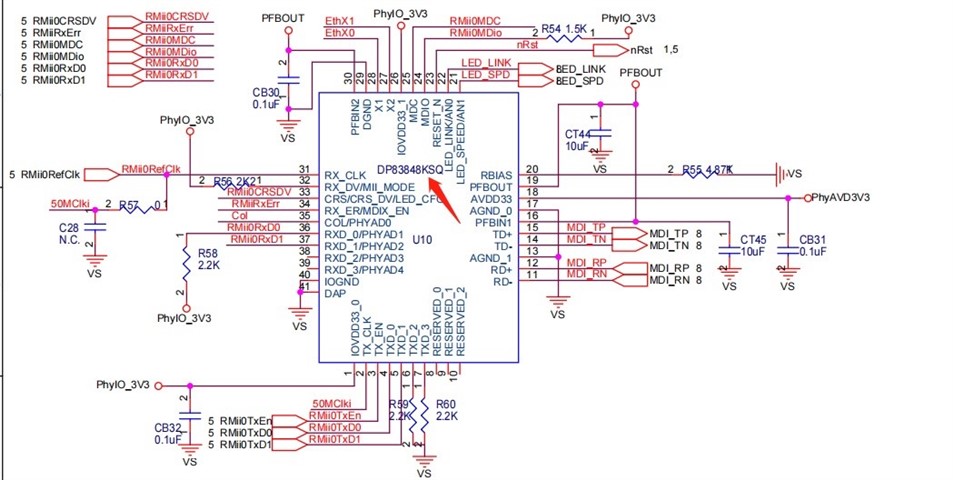

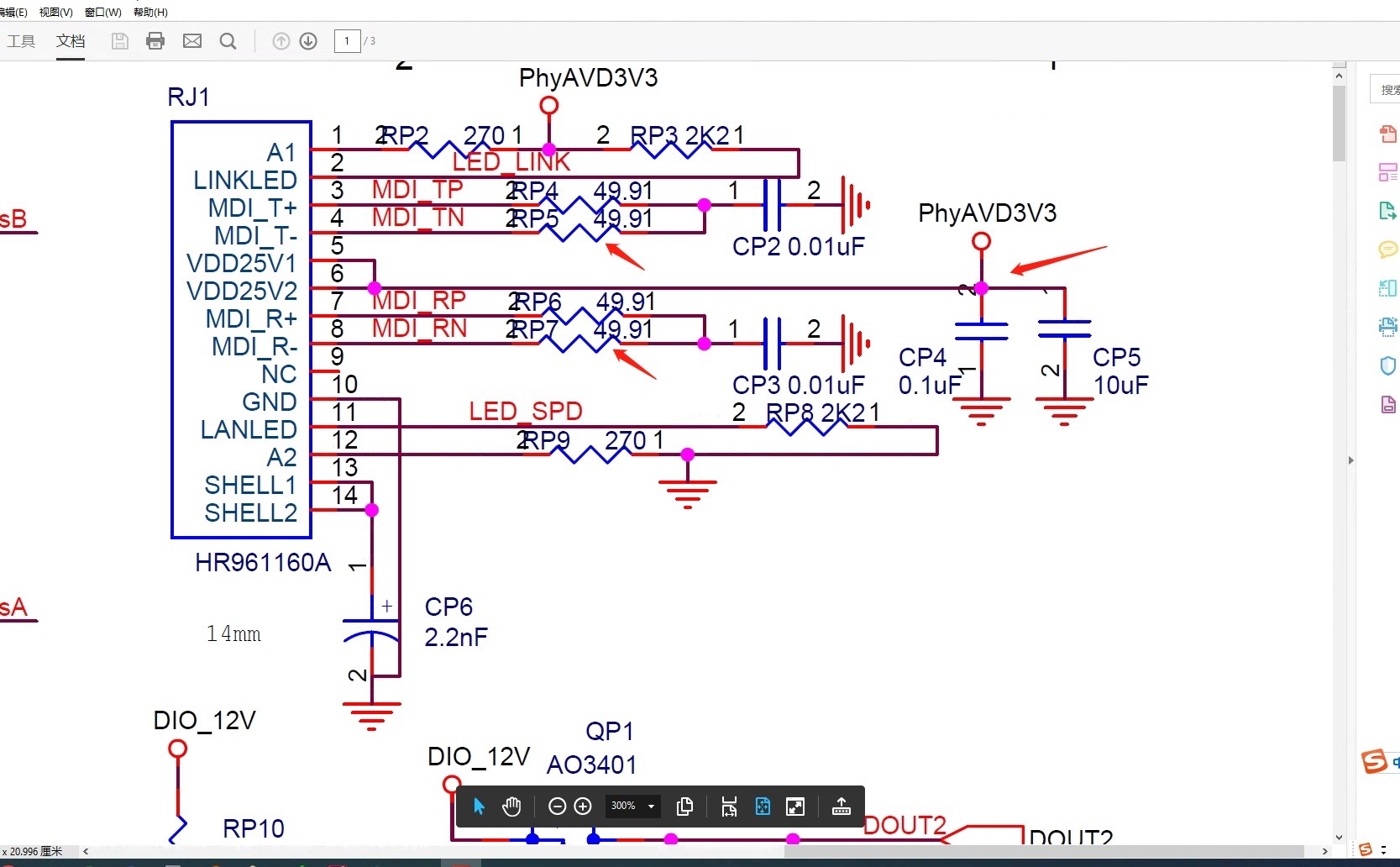

此 PHY83848KSQ 网络变压器① Ω 差分线为49.9R 且电容接地;②中心抽头连接到3.3V

此 PHY83848VVVBI 网络变压器通过51R 至3.3V 连接到差分线。 中心抽头通过0.1uF 电容器接地。 对于这种类型的 PHY、这两个选项中的哪一个是正确的?

谢谢!