Other Parts Discussed in Thread: TUSB1210, TUSB1210EVM

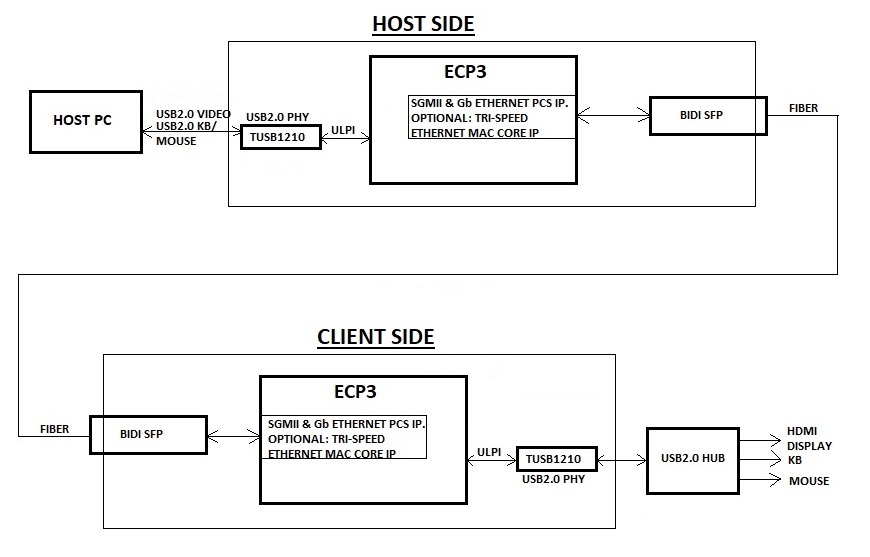

实现案例1和案例3。 对于情况1、使用 TUSB1210 PHY 通过 PHY ULPI 引脚连接 PC 主机和 FPGA;对于情况3、我使用另一个 TUSB1210 PHY 连接 FPGA 和外部 USB 集线器。

这是我对 TUSB1210EVM 的理解:

电源输入:

+5V 至 CN1.2和 CN1.4

+1.8V 至 CN1.19和 CN1.20

所有情况均采用高速模式。

案例1:如果我希望 TUSB1210连接到 PC USB 端口(USB 主机)、则必须将 TUSB1210设置为器件、数据表第53页。

案例2:如果我希望 TUSB1210连接到 USB 器件(鼠标或键盘等外设)、则必须将 TUSB1210设置为主机、数据表第48页。

案例3:如果我想连接 USB 集线器、集线器是否充当 USB "主机"、那么必须将 TUSB1210设置为器件????

对于案例1、如果我的上述假设是正确的、

我认为 J3跳线未使用、因此未组装。

J5跳线设置为1-3和2-4。 我看不到 J5:1-3的作用是什么、我认为这不是必需的。

J6跳线设置为1-2、时钟输出模式、使用板载26MHz 振荡器进行 REFCLK 输入。

J7跳线未组装。

J8跳线未组装、不确定其用途。

J9跳线设置为2-3、因此芯片通过+1.8V 启用。 我可以设置为1-2、以便在未连接 USB 电缆时芯片断电。

J11跳线未组装

当我将 USB 电缆从 PC USB 主机连接到用作器件的 TUSB1210 PHY、并向 CN1施加+5V 和+1.8V 电压时、我的电源指示+5V @ 0.04A 和+1.8V @ 0.15A。

我不希望+1.8V 电流消耗150mA、因为数据表显示在 HS 运行时运行、在 VBAT、VDDIO 和 VDD18之间总共只消耗48mA 的电流、数据表第7页。 为什么电流消耗如此大????

U5.20 VDD33读取+3.3V => U5.21 VBAT、确定

U5.12 VDD15读取+1.5V、正常

U5.17 CPEN 为低电平、好的原因是不希望 U2生成+5V 电压。

U5.22 VBUS 读取+5V、正常

U5.1 REFCLK 具有26MHz 时钟

U5.26时钟具有60MHz 输出时钟、好的

如果我实现上述情况2、我将从上面更改以下跳线:

J3 跳线设置为2-3、以将 U2.5 +5V 传递到 USB 电缆 VBUS 引脚

J5跳线设置为1-2和3-4。

是否必须组装 J8跳线、或者是否需要通过小于1k Ω 的电阻器将其接地????

U5.17 CPEN 信号在主机模式下变为高电平的原因是什么????

我感谢各位的评论。

谢谢、Roland