请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN65LVDS93A 主题中讨论的其他器件: DS90CF388、 DS90C3202

大家好、

我的客户希望使用 SN65LVDS93A 对来自 FPGA 的 SPI 信号进行串行传输。

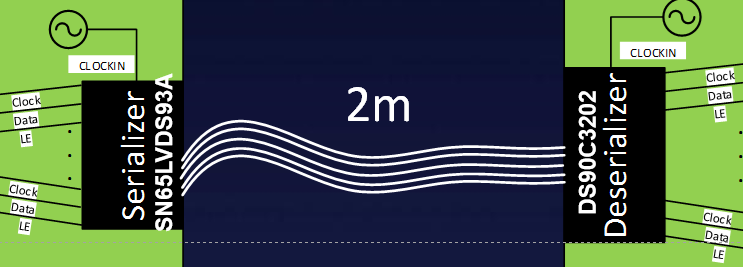

应用图如下所示:

数据速率约为100MHz、SPI 信号和时钟来自 FPGA GPIO。

电压电平为 CMOS3.3和 CMOS1.8或 LVDS

因此、有几个问题需要您的支持:

器件能否支持 SPI 信号的发送?

2.他们是否可以使用 FPGA GPIO 为器件生成时钟? 输入时钟是否有任何限制?

3.他们需要2m 电缆来传输数据,您能不能帮助 推荐电缆类型?

4.请帮助查看 DS90C302是否支持接收器应用?

4个 LVDS 输出之间的延迟有何不同?

Lacey

非常感谢!

非常感谢!