主题中讨论的其他器件: TMDS181

您好!

我们尝试在 FPGA kintex-7 XC7K70T-1中集成 Xilinx DisplayPort RX 子系统 v2.1、以接收 DP1.2流程。 (我们的应用需要将流程发送到两个 MiniDissays)。

我们需要使用4个通道、每个通道@5.4Gbps。

我们从头开始设计电路板,并按照 SLLA358应用手册安装了所需的 SN65DP159。

但我们面临着许多问题:

1)对于一个板(在下面的 SN02board 中)、我们能够协商 DP 链路、但有一些限制:

a)从不达到所需的最大值5.4Gbps

b)大部分时间设置为2.7Gbps、连接到在扩展坞上具有 DisplayPort 的 Windows 7戴尔笔记本电脑;当正确协商链路时、它工作良好、非常稳定。

c)切勿连接至具有 NVIDIA GPU 和本机 DisplayPort 输出的测试 PC

2)与第二个板(在 SN04板的后面)

a)切勿在5.4Gbps 或2.7Gbps 或更低的速率下运行

b)连接到笔记本电脑或测试 PC 的情况相同。

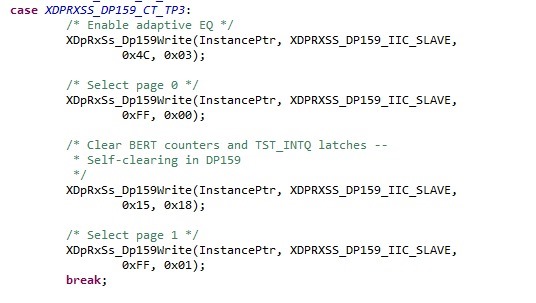

对于 SN02/SN04板、当链路不起作用时、我们使用 Xilinx 驱动程序中的诊断命令 XDpRxSs_ReportDp159BitErrCount (它读取重定时器寄存器)

我们已经看到重定时器输入端存在错误(建立链路时不会跟踪错误、实际上墨水非常稳定)。 请检查附加的日志,获取的设置为2.7Gbps,以使其也处于 工作状态(两个日志都与 SN02相关,SN04不正常与 SN02 1相同)。

有人能支持我们吗?

某些重定时器配置值是否不正确? 我们遵循了 Xilinx 参考设计中建议的配置

我们可以调查什么?

我们怀疑重定时器复位有问题:实际上、当 SN02正常工作时、如果我们对 FPGA 进行重新编程、即使我们多次执行此操作、链路也会正常工作。 相反、如果我们对电路板进行下电上电、有时链路正常、有时不正常。

非常感谢您的参与。 由于日程紧迫、我们非常着急

再见

Giovanna

登录韩语

(三

已成功运行 SPI 轮询示例

XCLR 变为低电平

===初始化===

XCLR 变为高电平

=== PS0 ===

(三

DisplayPort 直通演示

(C) 2015年由 Xilinx 提供

系统配置:

(三

= XDpRxSs_ReportCoreInfo =

DisplayPort RX 子系统信息:

DisplayPort 接收器(DPRX):是

IIC:是

已启用音频:否

支持的最大音频通道数:2.

每种颜色支持的最大位数:8.

支持的颜色格式:0

启用 HDCP:否

支持的最大通道数:4

支持的最大链接速率:20

多流传输模式:否(SST)

支持的最大流数:1.

DP RX 子系统在以下模式下运行:具有流1的 SST

系统功能设置为:LineRate A、LaneCount 4

秘书长的报告 R *********

在此配置中、RX 充当使用 TX 的主设备

显示在 RX 上接收到的视频。 该模式在上运行

DP159转发的时钟。 CPLL 用于 RX 和 TX

(三

VPHY PLS 0

VPHY PLS 0

RX 链路和信道功能设置为 A、4

------------------------------------

-- DisplayPort RX-TX 演示菜单 --

------------------------------------

选择选项

1 =更改通道和链路功能

2 =链路、MSA 和错误状态

3 =切换 HPD 以要求重新培训

4 =重新启动 TX 路径

5 =将 TX 数据切换到内部图形发生器

6 =将 TX 切换回 RX 视频数据

W =灌电流寄存器写入

R =读取接收寄存器

Z =再次显示此菜单

x =返回主菜单

------------------------------------

请插入 RX 线缆以开始培训...

VPHY PLS 0

Dprx_InterruptHandlerPwr

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :0

BERT counter0[11:8]:0

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0xA、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0x6、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0xA、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0x6、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0xA、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0x6、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0xA、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0x6、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0xA、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0x6、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

链路速率:0xA、通道数:4

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :255

BERT counter0[11:8]:15.

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT c

----------

日志确定

--------

(三

已成功运行 SPI 轮询示例

XCLR 变为低电平

===初始化===

XCLR 变为高电平

=== PS0 ===

(三

DisplayPort 直通演示

(C) 2015年由 Xilinx 提供

系统配置:

(三

= XDpRxSs_ReportCoreInfo =

DisplayPort RX 子系统信息:

DisplayPort 接收器(DPRX):是

IIC:是

已启用音频:否

支持的最大音频通道数:2.

每种颜色支持的最大位数:8.

支持的颜色格式:0

启用 HDCP:否

支持的最大通道数:4

支持的最大链接速率:20

多流传输模式:否(SST)

支持的最大流数:1.

DP RX 子系统在以下模式下运行:具有流1的 SST

系统功能设置为:LineRate A、LaneCount 4

秘书长的报告 R *********

在此配置中、RX 充当使用 TX 的主设备

显示在 RX 上接收到的视频。 该模式在上运行

DP159转发的时钟。 CPLL 用于 RX 和 TX

(三

VPHY PLS 0

VPHY PLS 0

RX 链路和信道功能设置为 A、4

------------------------------------

-- DisplayPort RX-TX 演示菜单 --

------------------------------------

选择选项

1 =更改通道和链路功能

2 =链路、MSA 和错误状态

3 =切换 HPD 以要求重新培训

4 =重新启动 TX 路径

5 =将 TX 数据切换到内部图形发生器

6 =将 TX 切换回 RX 视频数据

W =灌电流寄存器写入

R =读取接收寄存器

Z =再次显示此菜单

x =返回主菜单

------------------------------------

请插入 RX 线缆以开始培训...

VPHY PLS 0

Dprx_InterruptHandlerPwr

Dprx_InterruptHandlerLinkBW

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :16

BERT counter0[7:0] :0

BERT counter0[11:8]:0

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

Dprx_InterruptHandlerPllReset

0 0 0

Dprx_InterruptHandlerTrainingDone

>中断:训练完成!!!(BW:0xA、通道:0x4、状态:0x77;0x77)。

Dprx_InterruptHandlerNoVideo

Dprx_InterruptHandlerVideo

20个空白

200个空白

= XDpRxSs_ReportLinkInfo =

DPCD = 0xA 中的 LINK_BW_SET (0x400)状态

DPCD = 0x4中的通道数设置(0x404)状态

DPCD = 0x77中的 LANE0_1_STATUS (0x043C)

DPCD = 0x77中的 Lane2_3_status (0x440)

SYM_ERR_CNT01 (0x448)= 0x80008000

SYM_ERR_CNT23 (0x44C)= 0xFFFFFFFF

PHY_STATUS (0x208)= 0xF000FF

= XDpRxSs_ReportMsaInfo =

RX MSA 寄存器:

时钟,H 总计 (0x510):1800

时钟,V 总计 (0x524):1375

HSyncPolarity (0x504):0

VSyncPolarity (0x518):0

HSYNC 宽度 (0x508):16

Vsync 宽度 (0x51C):5.

霍尔兹分辨率 (0x500):1600

垂直分辨率 (0x514):1200

Horz Start (0x50C):48

垂直开始 (0x520):119

Misc0 (0x528):0x00000021

Misc1 (0x52C):0x00000000

用户像素宽度 (0x010):4.

M VID (0x530):288358

N VID (0x534):524288

M AUD (0x324):0

N AUD (0x328):0

VB-ID (0x538):16.

= XDpRxSs_ReportDp159BitErrCount =

LOCK_STATUS :64

TST_INT/Q :0

BERT counter0[7:0] :0

BERT counter0[11:8]:0

BERT counter1[7:0] :0

BERT counter1[11:8]:0

BERT counter2[7:0] :0

BERT counter2[11:8]:0

BERT counter3[7:0] :0

BERT counter3[11:8]:0

***检测到的分辨率:1600 x 1200***

周期0

Dprx_InterruptHandlerVideo

Dprx_InterruptHandlerVideo

Dprx_InterruptHandlerVideo

***检测分辨率:1600 x 1200 @ 60Hz,BPC = 8,颜色= 0***

选择 Format 1 4:3 24位 RGB 60.00P

型号1600 1200 1800 1375 152 134 16 5 32 36 48 0.323 60.00 12.121 148.500 4车道 x 2.

SPI_CHECK 失败偏移量0x07、预期为0x10、读取为0x00

SPI_CHECK 失败偏移量0x33、预期为0x67、读取为0x74

SPI_CHECK 失败偏移量0x80、预期为0x00、读取为0x01

SPI_CHECK 失败偏移量0x81、预期为0x00、读取为0x81

SPI_CHECK 失败偏移量0x9A、预期为0x0F、读取为0x00

等待大约1000 us

=== PS1 ===

=== PS2 ===

=== PS cancel ===