主题中讨论的其他器件: DS100DF410

大家好、这是我的第一篇文章。

我们正在考虑使用 DS100DF410EVK 的10GbE 重定时器。

可使用哪些设置来减少抖动?

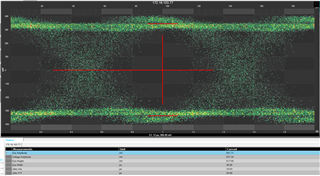

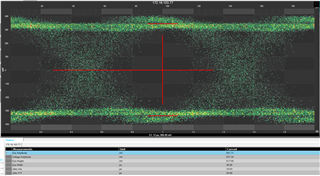

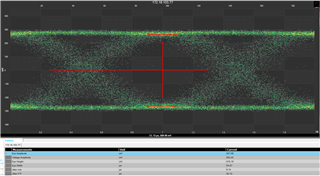

以上是输入眼图波。

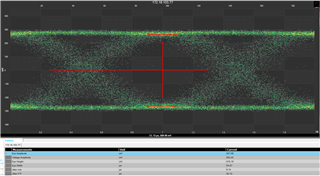

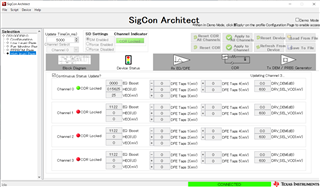

以上是通过 DS100DF410EVK 的输出眼图波。

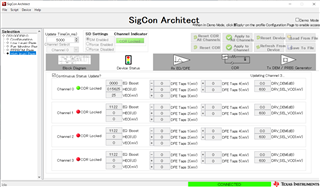

当前 SigCon 状态如下。

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、这是我的第一篇文章。

我们正在考虑使用 DS100DF410EVK 的10GbE 重定时器。

可使用哪些设置来减少抖动?

以上是输入眼图波。

以上是通过 DS100DF410EVK 的输出眼图波。

当前 SigCon 状态如下。

谢谢。

您好、Sim、

可用于减少抖动的主要重定时器设置是发送去加重和 CDR 带宽。 此时、调整 CDR 带宽似乎是最合适的操作、因为它看起来不需要去加重。

为了了解调整 CDR 带宽是否有用、请使用 BERT 生成信号并在信号中启用各种抖动、这一点很有价值。 通过执行此操作、您可以观察重定时器是否按预期响应抖动。

此时、您是否对从重定时器 TX 观察到的眼图张开度有疑问?

谢谢、

Drew

您好、Sim、

我认为您的测量值与重定时器 CDR 带宽非常相关。 默认情况下、它大约为5MHz、因此 CDR 不会跟踪抖动> 5MHz 是合理的。

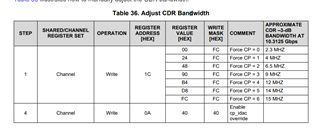

CDR 带宽是可调的(见下文)、但不能降低至1MHz。 下面的屏幕截图摘自我们的10G 重定时器编程指南、下面也链接了该指南。

https://www.ti.com/lit/pdf/snla323

谢谢、

Drew