主题中讨论的其他器件: SN65DSI83、 DSI 调谐器

您好!

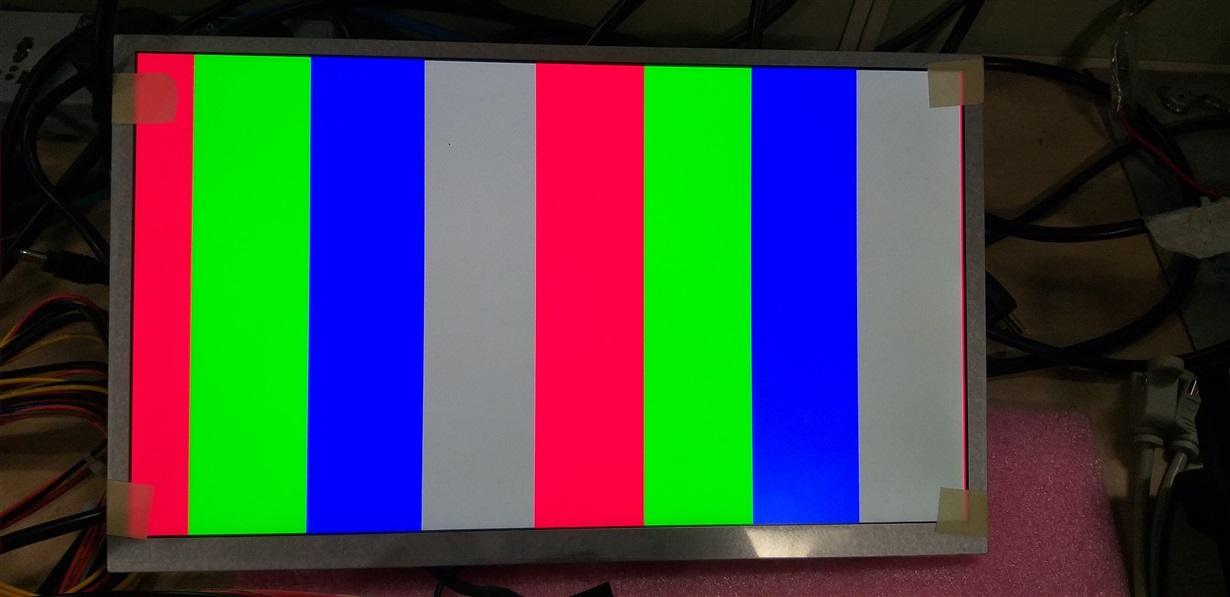

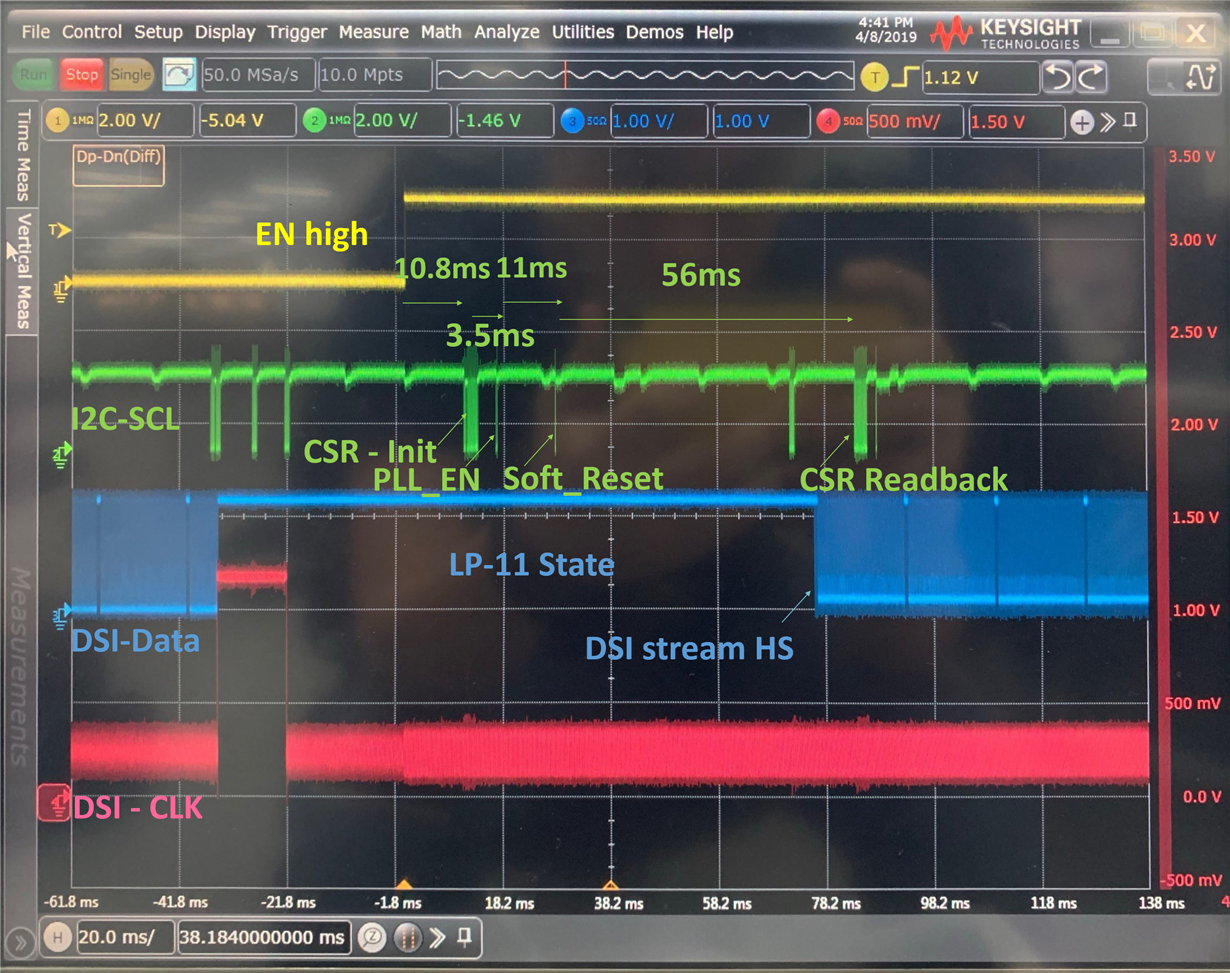

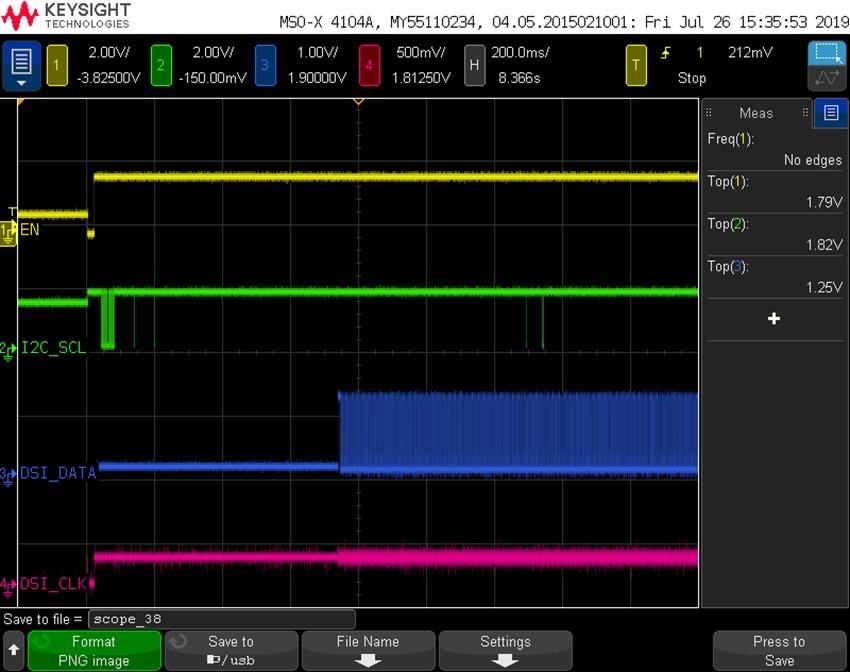

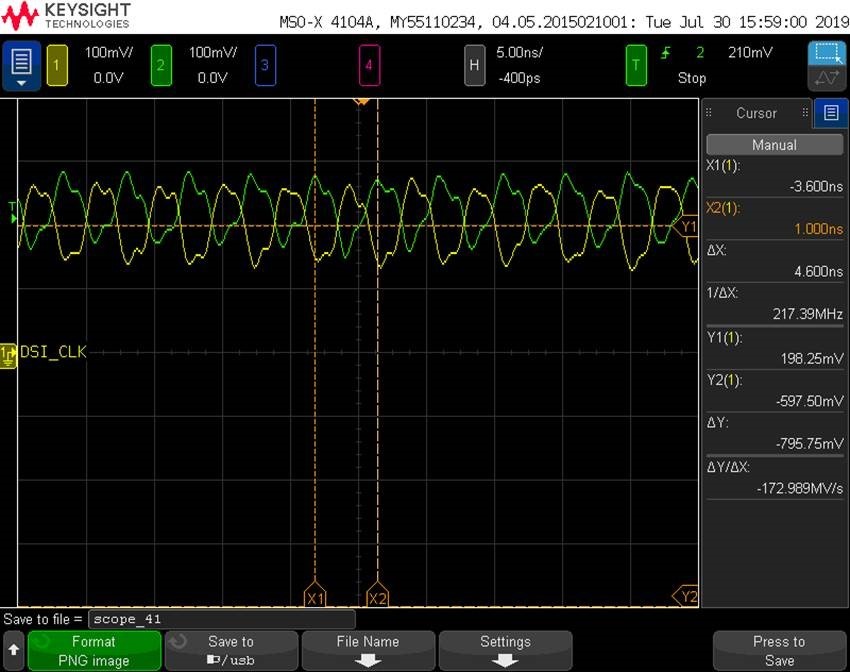

我们使用的是自定义电路板、它具有 MIPI DSI 转 LVDS 桥接器(SN65DSI84)以提供 LVDS 显示。

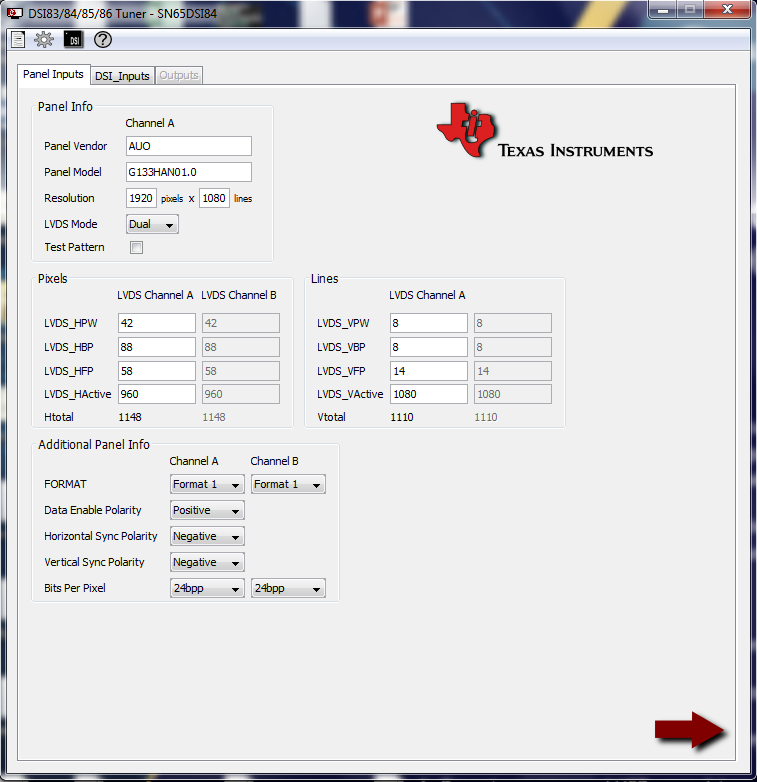

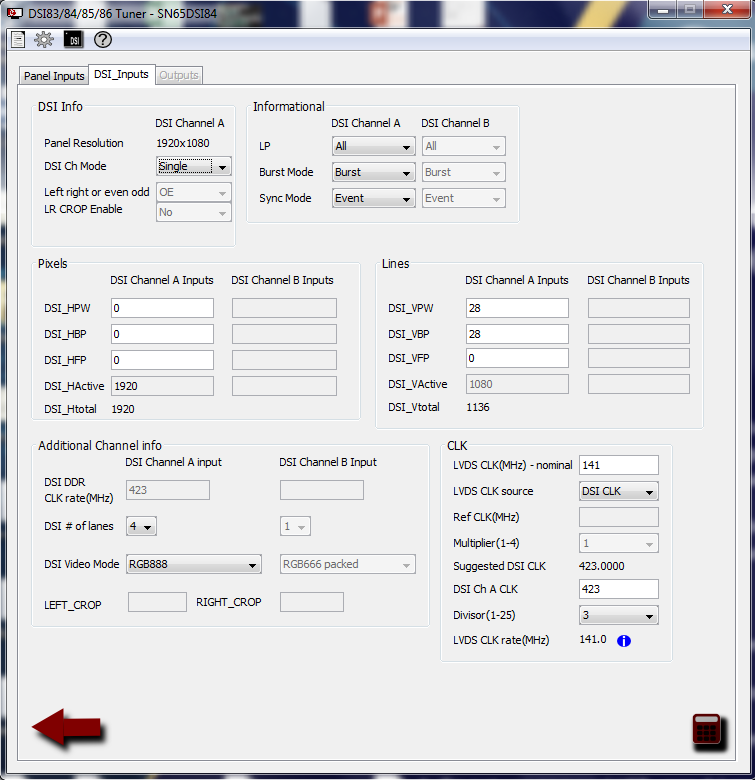

我们需要启动双通道 LVDS 显示(G133HAN01.0 AUO)。 LVDS 面板 像素时钟范围为134 MHz 至149 MHz。

我们已根据数据表配置面板输入和 DSI 输入、以生成 CSR 值。 但是、即使 DSI 时钟速率为423MHz、我们也会收到一条警告消息"DSICLK 速率应小于500m"。

已附上 DSI 调谐器配置图片供您参考。

- 我们的配置是否正确?

- 我们是否可以跳过此警告消息?

- 我们如何克服这一警告信息?

请提供您的反馈。

谢谢、

安东尼