您好!

关于使用 DS125DF1610时的 CDR 锁定、我有一些问题无法解释。 下面是我的设置:两个 FPGA 之间的 SERDES 链路、两个 FPGA 之间的 DS125DF1610。

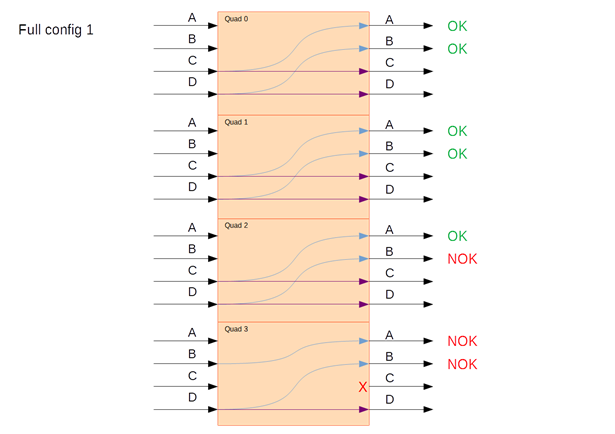

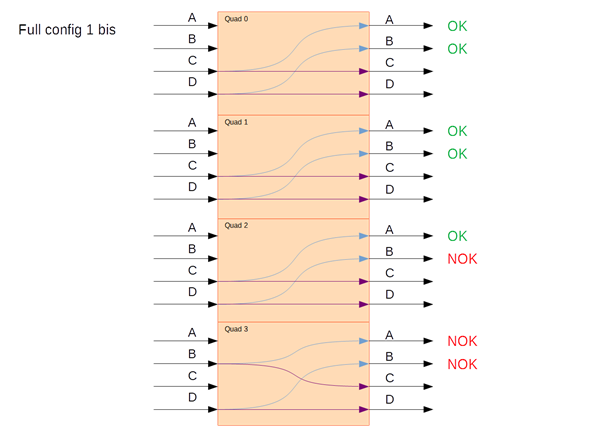

DS125DF1610交叉点开关采用这种方式进行设置(在过程中可能会发生变化、但初始设置会导致问题的开始):

首先、我想将允许获取锁定的通道(使用共享寄存器0x0F 和0x10)限制为我需要的通道、即每个四通道上的通道 A 和 B (TX)。

第一个问题:我很快意识到、为了锁定 CDR、对于每个通道、我必须同时允许 TX 通道和 RX 通道锁定。 这使我 允许锁定除四通道3 (完全配置1)中的通道 C 以外的所有通道。

然后、我在四通道3中遇到了第二个问题:当每个通道都被锁定且每个链路都正常工作时、以某种方式关闭通道 D RX 源上的信号会导致通道 B TX 丢失 CDR 锁定和信号检测(如预期的那样) 但也会导致通道 A TX 丢失 CDR 锁定、同时信号检测仍在运行。 通道 B RX 上的信号未修改。 我注意到、如果我允许通道 C 锁定、将共享寄存器0x0F 和0x10重置为默认值0xF (配置1 bis)、问题就会得到解决。 我不明白原因,但问题得到解决。 继续。

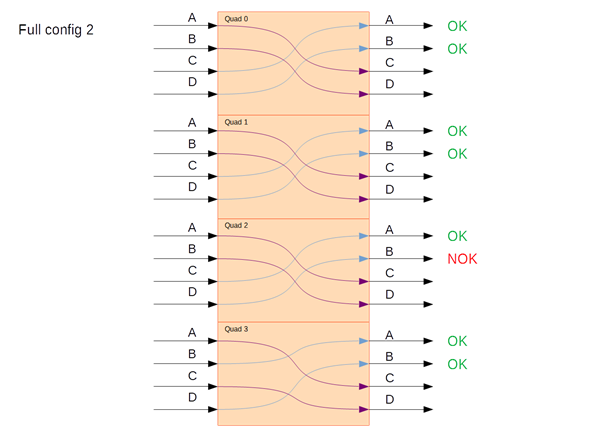

初始设置正常、所有通道均已锁定、所有链路均正常工作。 第三个问题是当我关闭所有 RX 通道源上的信号然后再次打开时:除四通道3的通道 A 和 B 之外、所有通道都成功重新锁定。 四通道2的通道 B 也有重锁故障、但没有系统地重锁。 我怀疑 DS125DF1610中交叉点的广播功能有问题、并尝试完整的配置2、其中每个 RX 通道仅路由到一个 TX 通道。

这解决了四通道3上的问题、我也不明白原因。 但第四个问题仍然存在、即四通道2的通道 B TX 在通道 C RX 的源极上关闭并再次打开信号时频繁(但不是始终)无法重新锁定。 我再次尝试使用允许锁定的通道、使用允许的并发锁定限制(共享寄存器0x05[3:0])、交叉点参数(本地和多驱动缓冲器、主/从功能...)以及本论坛相关主题中建议的 EQ 增强参数 (尝试 CLTE 调整模式1而不是0、然后返回到0并尝试几个 EQ 升压值)、结果无效。 此时、我不明白正在发生什么、我已经没有尝试的选项了。

为了排除该问题的其他原因、我还进行了此测试:对于四通道2的通道 B TX、将 FIR 滤波器输入设置为原始数据而不是标准重定时数据(通道寄存器0x1E[7:5]设置为0b000、而寄存器0x09[5]设置为1)。 这种方式对于接收 FPGA 而言、信号太弱、我使用 FIR 滤波器主滤波器、前体和后体抽头对其进行放大(通道寄存器0x3D、0x3E 和0x3F 分别设置为0x3F、0x49和0xD5)。 我知道,这是丑陋的,不可靠的,我肯定不会永久保留这种设置。 但它允许我在四通道3 TX 通道 B 的 CDR 解锁时恢复功能链路。

我使用的是通过8个 DS125DF1610以菊花链形式连接的25MHz 参考时钟(始终已成功锁定)、10.3125Gbps 比特率、无 CLTE 适配(手动设置 EQ 增强功能、并保持不变)、无 DFE。 仅在四通道3的通道 B TX 上反极性。

我在多个电路板上遇到了这些问题、导致我排除了硬件故障。 有时链路正常工作这一事实似乎表明电路板或路由没有任何问题。 我很确定我在设置 DS125DF1610的过程中缺少什么、或者我无法理解它应该如何工作。 我在这里做了些什么问题吗?

此致、

--

Romain Ducaffy