主题中讨论的其他器件: TCA6424A、 LM2596

你好!

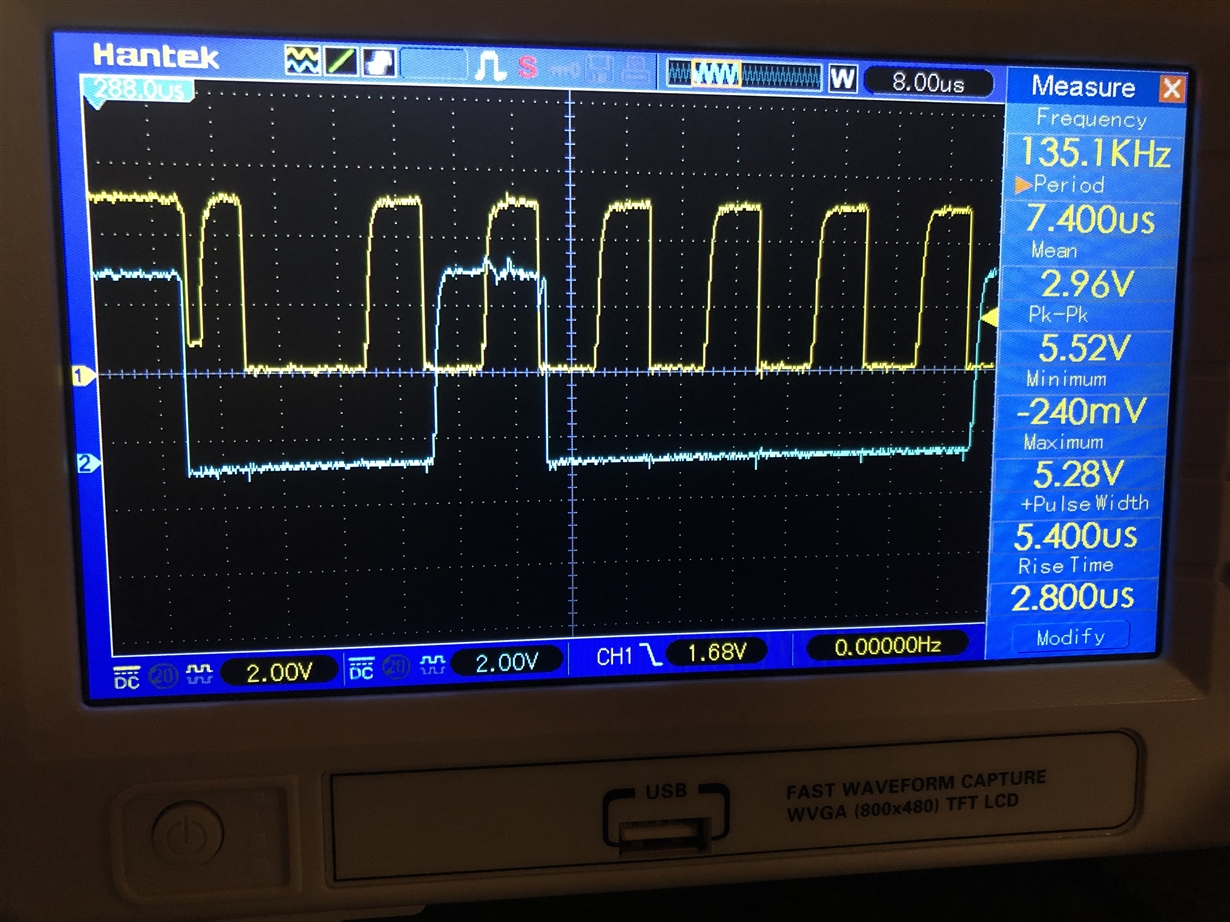

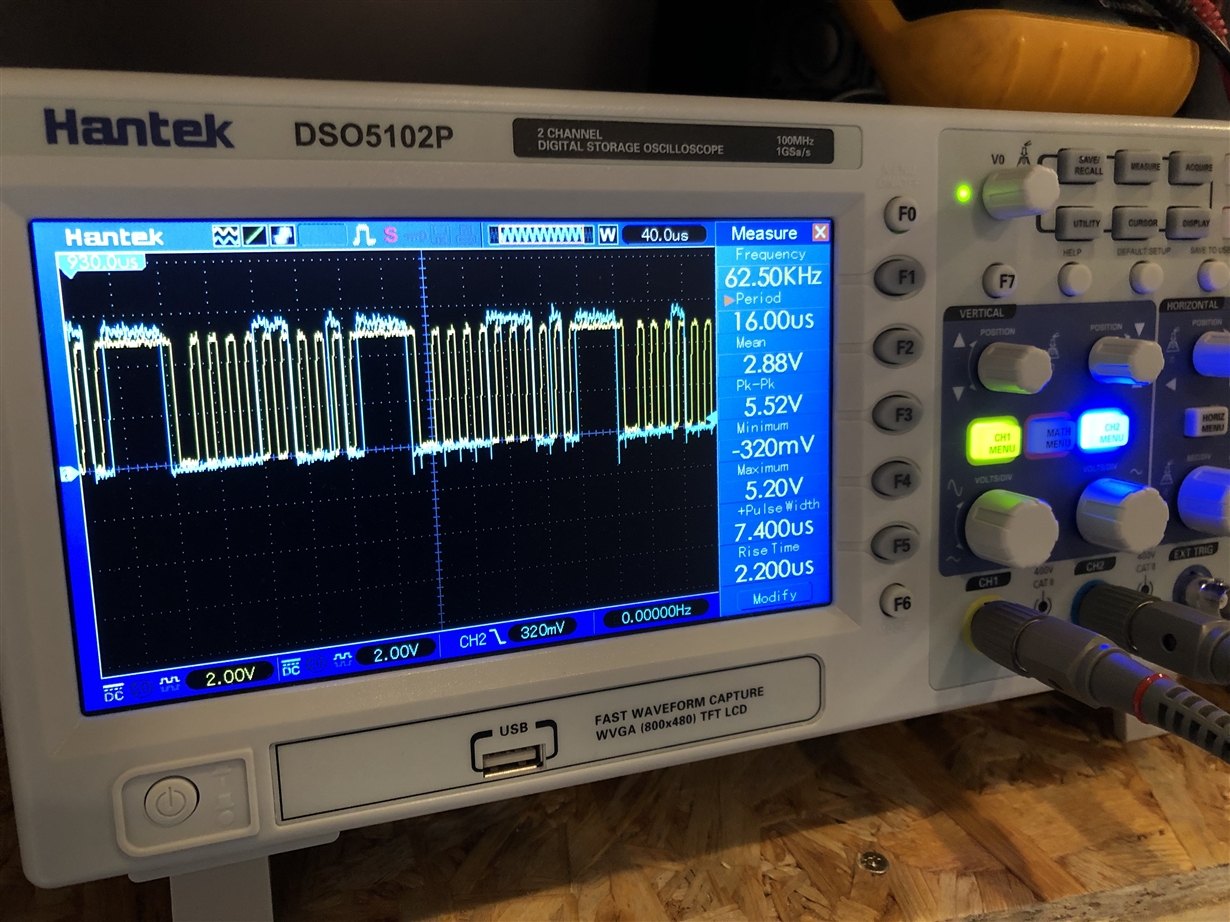

在 SDA 线路进入启动条件的同时、我在 SCL 线路上有一个奇怪的下降尖峰。 请看一下图片。

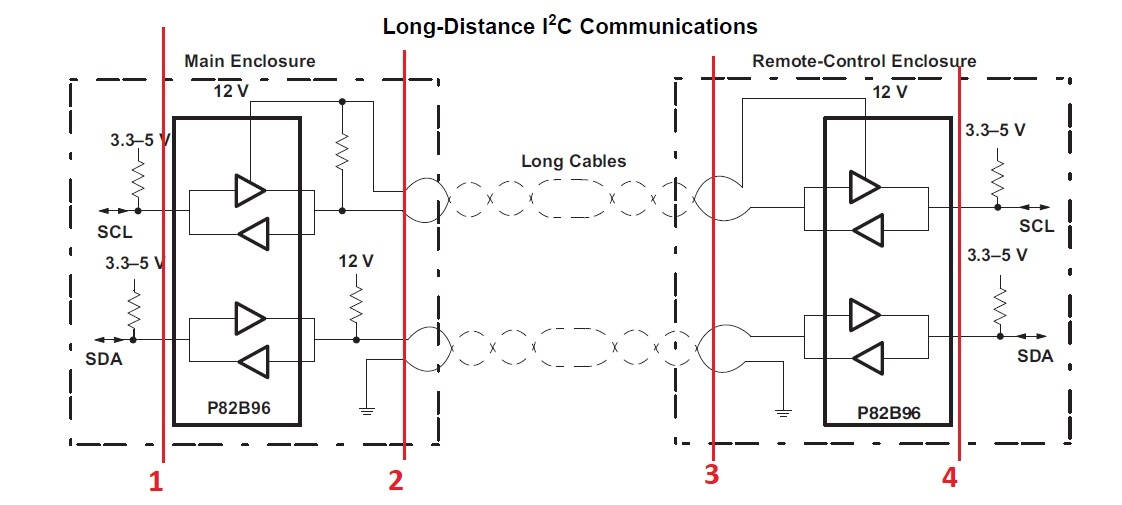

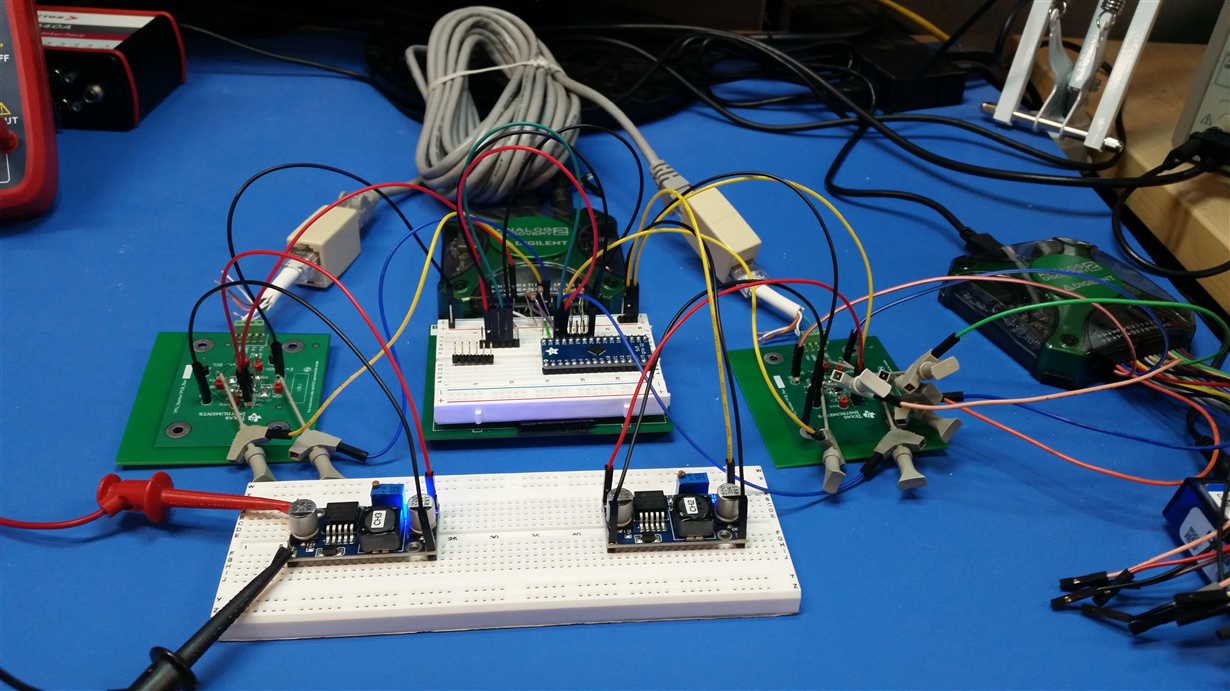

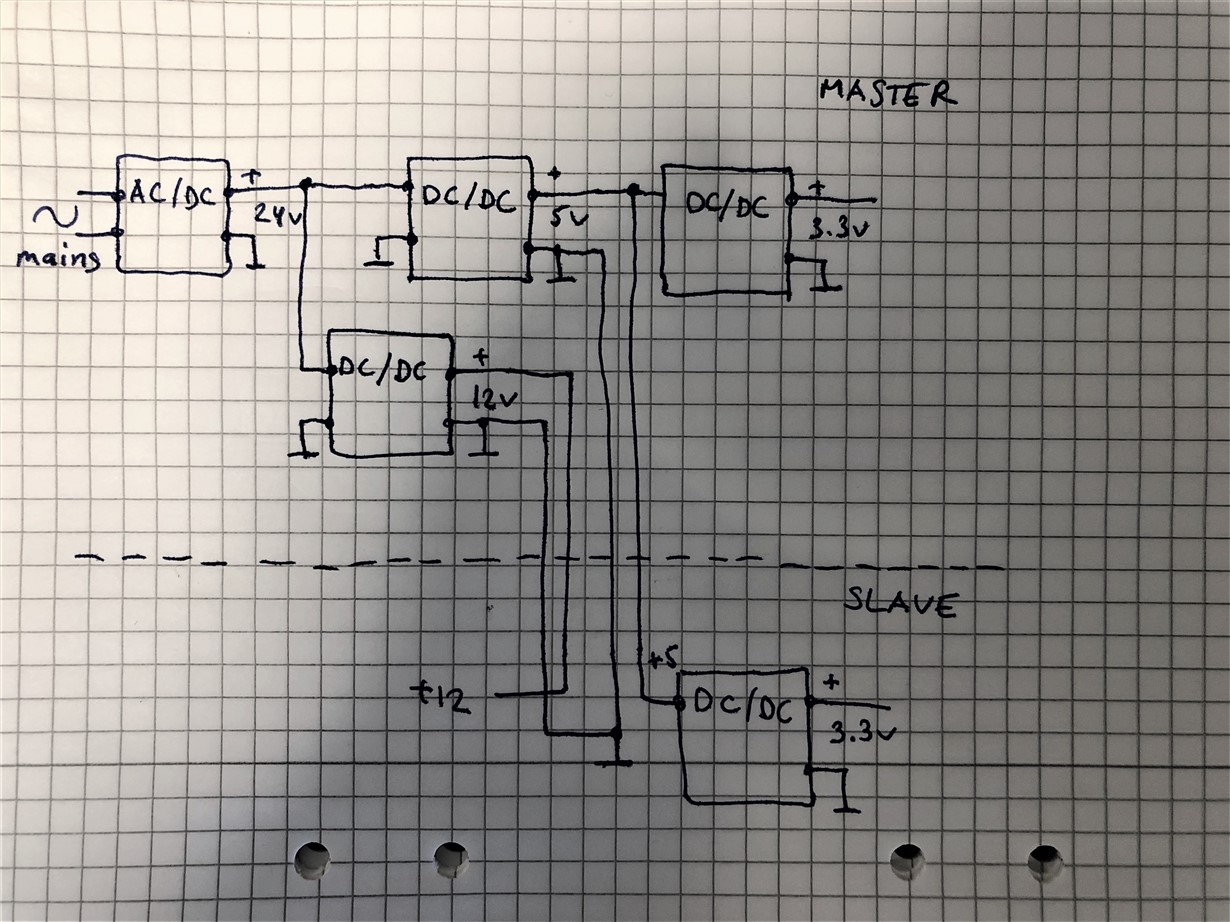

我最初的设置是一个 I2C 主设备(Raspberry PI)、主板上有一个从设备(MCP23017)和 P82B96、4个从设备板以星形拓扑连接、每个分支有一根 CA 10 m CAT6电缆。 每个从属电路板都有自己的 P82B96和 MCP23017。 我还在主器件侧使用了逻辑电平转换器(3.3V/5V)。

由于上述问题、我减少了故障排除设置、现在它符合以下标准图:

电缆的中等长度约为5-7米、为 CAT6。

如果我绕过 P82B96将从板直接连接到 I2C 主设备(Raspberry PI)、一切对我来说都正常、I2C 主设备可以看到从设备。

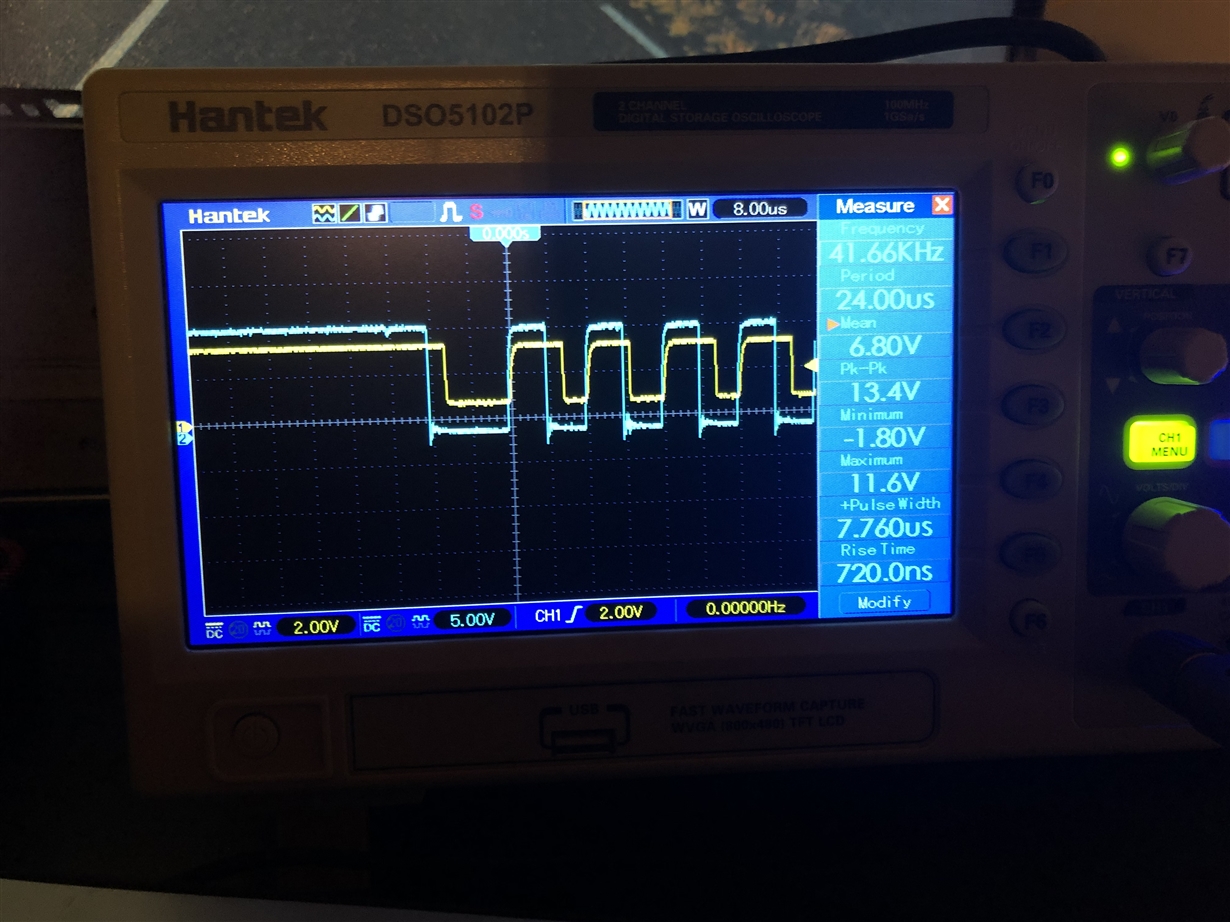

如果我断开远程侧的电缆、从而使主 P82B96具有电缆和上拉电阻器、一切看起来也正常。

只有当我将所有东西连接在一起时、才会出现问题。 请注意、在所有点1到4中都可以观察到上述下降尖峰(图中为红色)。

我尝试使用上拉电阻器、但它没有改变任何东西。 现在、我在 I2C 侧4K7和总线侧(仅主器件) 470R 上有上拉电阻器。

我还尝试通过一条单独的电缆携带 SCL、怀疑来自 SDA 的串扰、但它根本没有改变任何东西。 尖峰是绝对持续的、而不是零星的。 这表明存在某种设计行为。

我检查了几次接线、一切似乎都正常。 我目前不是很好:-)