您好!

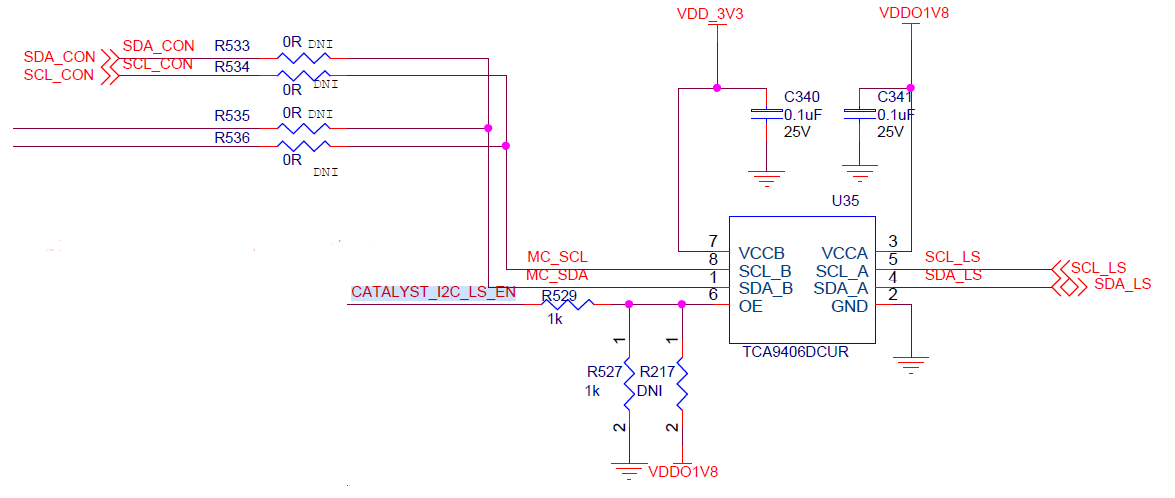

我们使用 TCA9406将 I2C 线路从3.3V 转换为1.8V。 下面是原理图:

我们在 SCL 和 SDA 的 VCCB 侧还有额外的10k 上拉电阻器。 下面是我们面临的问题:

1) 1)当我们用10k 连接 R217并移除 R529、R527时、这相当于将 OE 连接到 VCCA。 在这种情况下、信号始终为高电平、主器件无法下拉线路。

2) 2)当我们连接 R529、R527并断开 R217时、我们将使用由3.3V IO 驱动的 Catalyst I2C_LS_EN 信号来控制 OE 引脚。 在此配置中、我们将在启用 VCCA 和 VCCB 后启用 OE 31ms。 在这种情况下、发生了与1相同的情况。 如果我们在启用 OE 之前将延迟增加到180ms、电路将按预期工作。 根据数据表、启用 OE 后等待200ns 足以使 O.S 稳定。

这个问题只在我们在 VCCA 侧连接从器件时发生。 当从设备未连接时、没有问题。

我们还观察到、在另一个电路板上、SCL_A 和 SDA_A 由4.7K 电阻器从外部上拉、OE 连接到 VCCA、因此工作正常。 但有问题的电路板也无法与外部上拉电阻器配合使用。

为何需要在启用 OE 时提供额外延迟?

我们有一些板、其中 OE 直接连接到 VCCA、而我们无法选择控制 OE。 这些电路板上也存在同样的问题。