Other Parts Discussed in Thread: ALP, DS90UB926Q-Q1

主题中讨论的其他器件:ALP、 DS90UB926Q-Q1

您好 TI 团队。

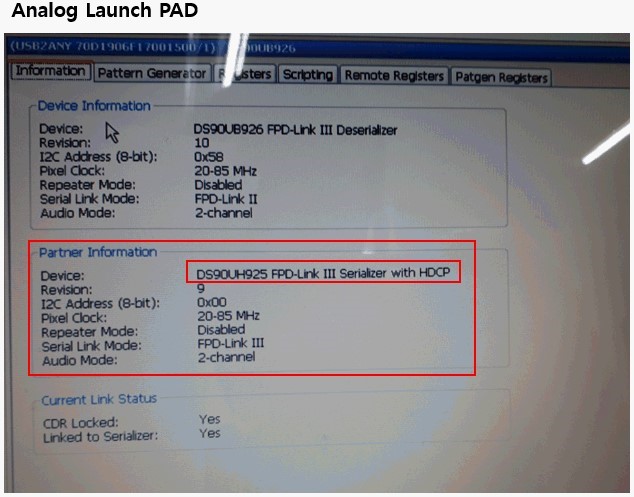

DS90UB926EVM 和 DS90UR905的连接方式如下所示。

ALP 将 DS90UR905识别为 DS90UH925。

1.这是否有问题? 还是 正常工作?

2.单独测试 DS90UB926EVM 时、运行 ALP 图形发生器不会产生数据输出。 如果它正常工作、是否应输出数据?

请检查我 的问题。

谢谢、

Downey。