大家好、

TUSB4041I 数据表显示了以下内容、并希望提出两个问题。

(第14页)

8.3.5晶体要求

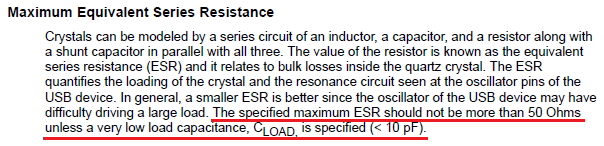

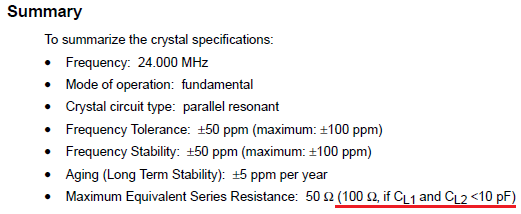

晶体必须是基波模式、负载电容为12pF 至24pF、频率稳定性额定值为±100PPM 或更高。 为 Ω 正确的启动振荡条件、TI 建议最大晶振等效串联电阻(ESR)为50m Ω。 如果使用晶体源、则使用并联负载电容器。

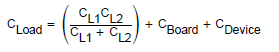

使用的确切负载电容值取决于晶体供应商。 有关如何确定负载电容值的详细信息、请参阅应用手册《德州仪器(TI) USB 2.0器件的晶体选择和规格》(SLLA122)。

1)

请 Ω SLLA122、如果负载电容(CLOAD)< 10pF、我了解50 μ F 的最大晶振等效串联电阻(ESR)不是强制性要求。

我的理解是否正确?

在这种情况下、请获取振荡裕度即可。

2)

您能否告诉我为什么 TUSB4041I 的负载电容下限为12pF? 这是强制性要求吗?

>晶体必须是基波模式,负载电容为12pF 至24pF

Ω 问题的背景是、我的客户希望使用 ESR 超过50 μ F 的小型晶体、因为电路板空间有限。

他希望增加晶体的选择数量。

此致、

雅丽塔