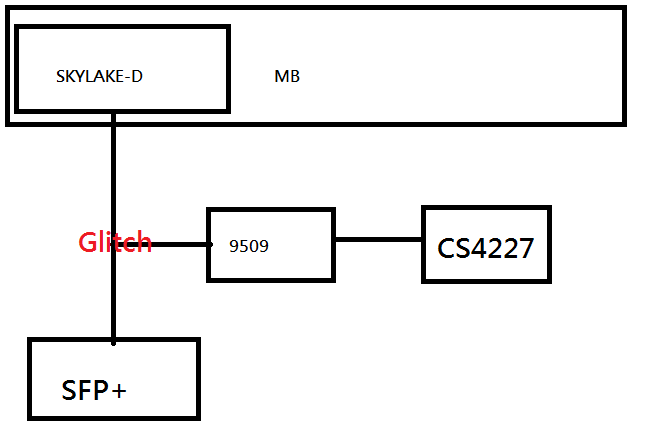

Other Parts Discussed in Thread: TCA9617B, TCA9617A, TCA9509

主题中讨论的其他器件: TCA9617A、 TCA9509

您好、Sirs、

需要您的评论。

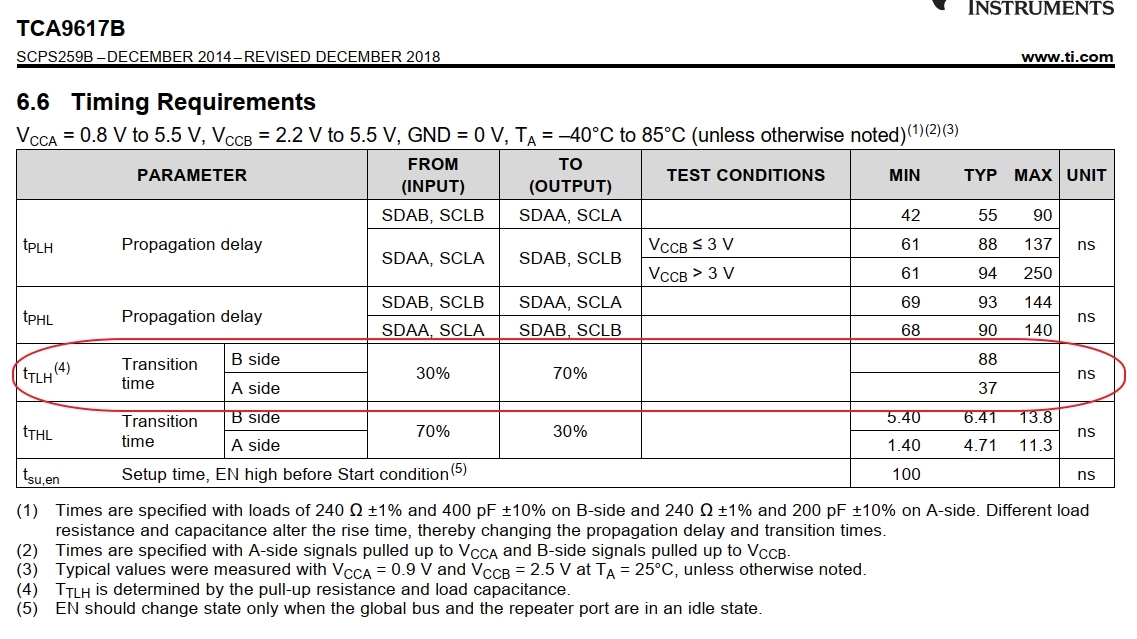

请参阅 TCA9617B 数据表8.3.2和6.6时序要求、

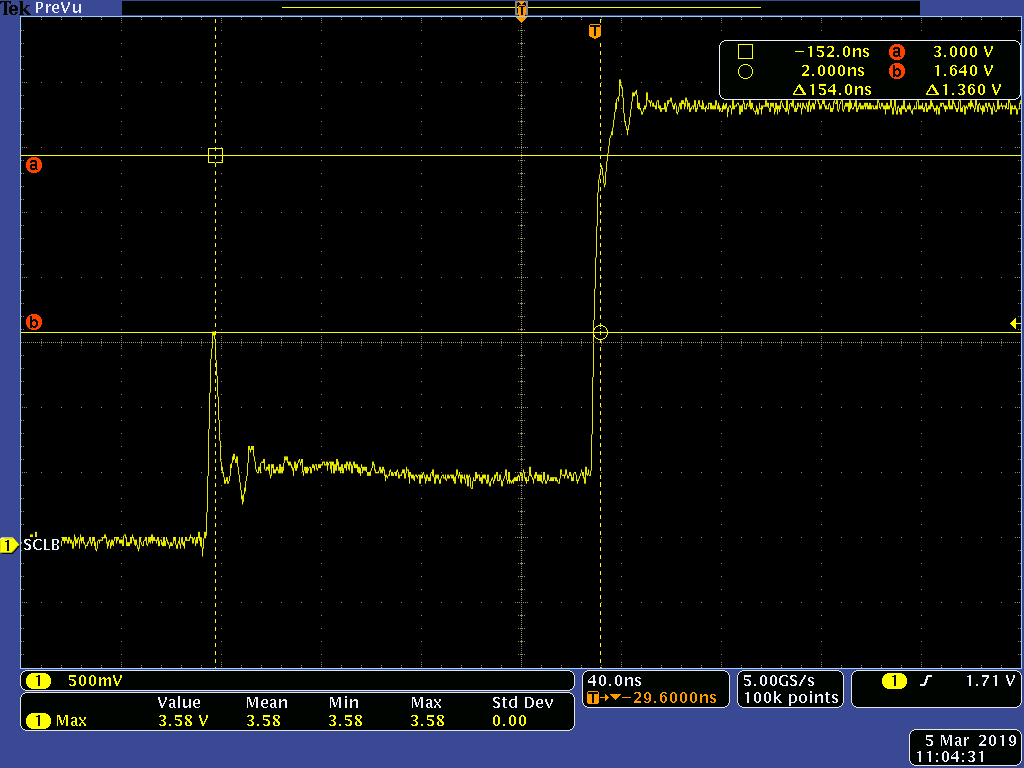

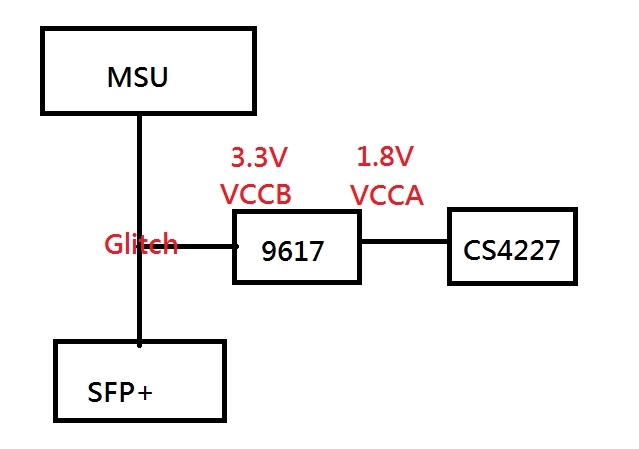

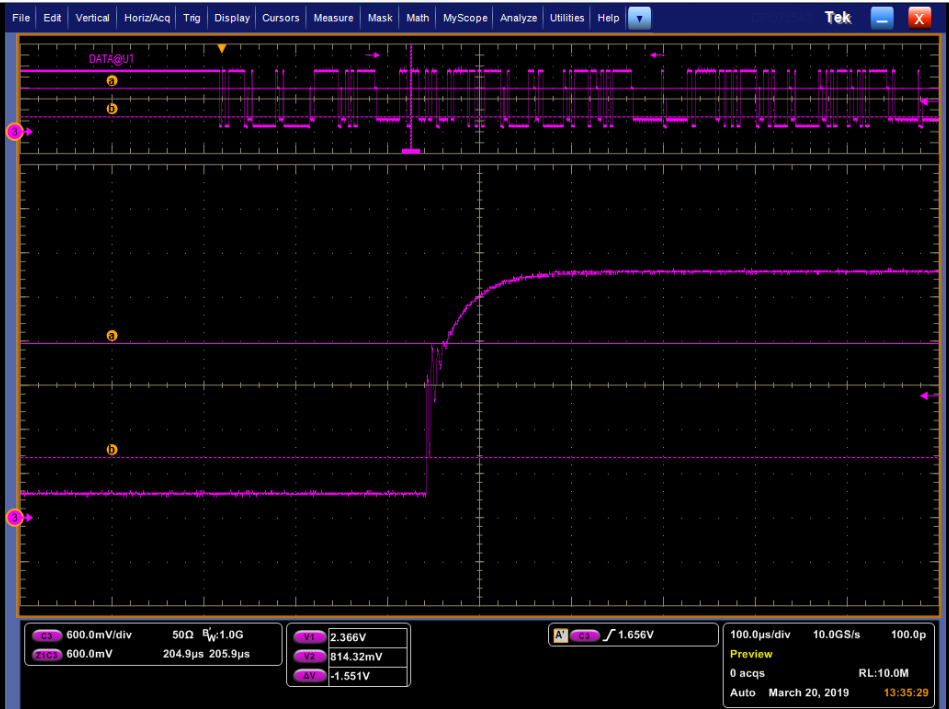

-如果 上升时间与附加波形(B 侧和100K 上拉电阻器)过快,问题是什么?

-作为波形,基座电压设置后会出现过冲。 如何消除它?

非常感谢!

由于 B 侧基座的性质和静态偏移电压、B 侧将存在轻微的过冲

从外部驱动低电平上升至0.5V 偏移。 TCA9617B 旨在控制此行为

前提是系统的上升时间大于20ns。 因此、应注意限制

当 B 侧有具有上升时间加速器的器件时、上拉强度。 过冲过大

如果过冲超过、B 侧基座可能会导致具有上升时间加速器的器件过早跳闸

加速器阈值。 由于 A 侧没有静态偏移低电压、因此在 Aside 上看不到基座、如图7所示。

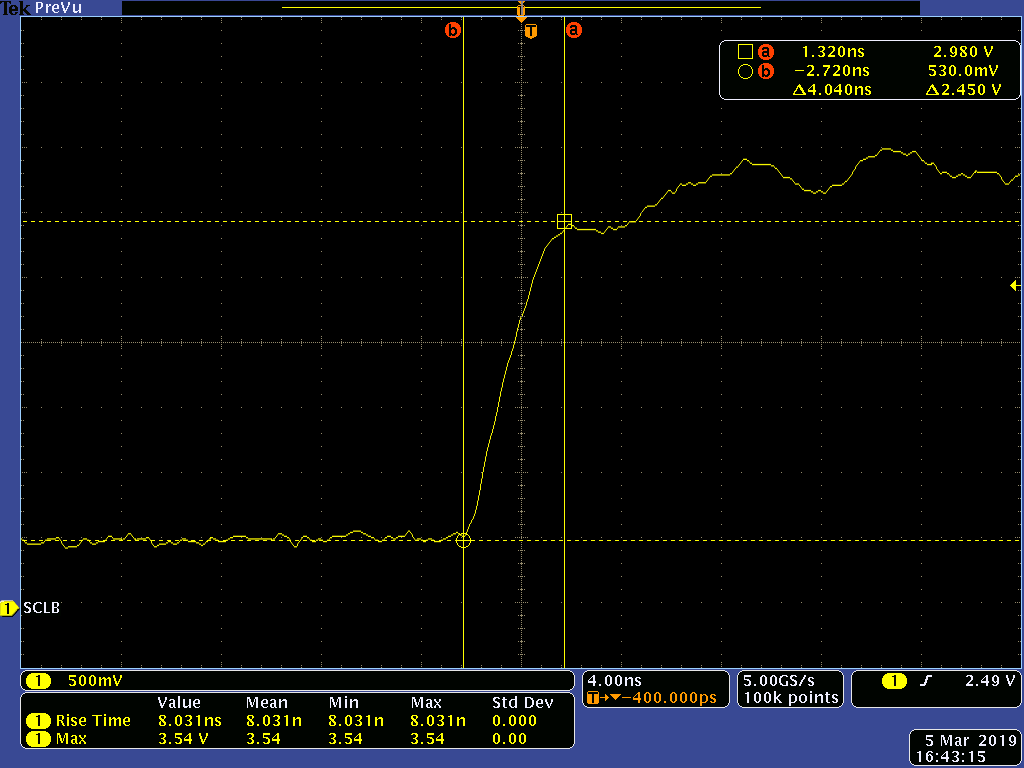

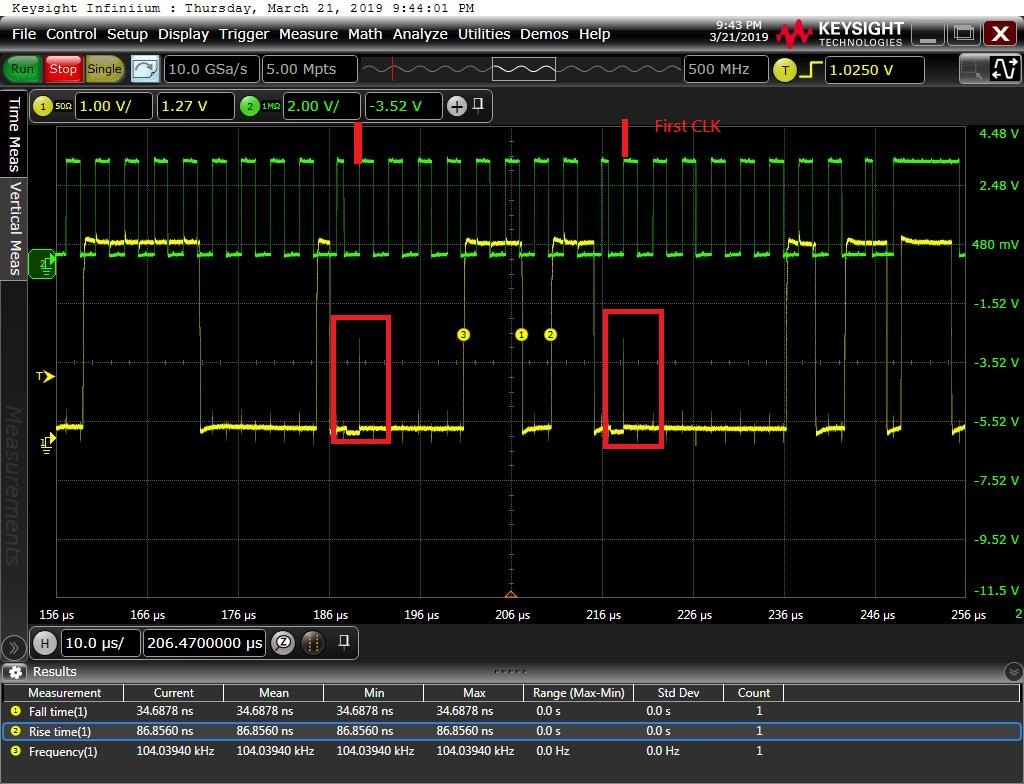

放大以查看有关上升时间的更多详细信息: