Other Parts Discussed in Thread: SN65LV1023A, SN65LV1224B, SCAN921224

主题中讨论的其他器件:SN65LV1023A、 SCAN921224

您好!

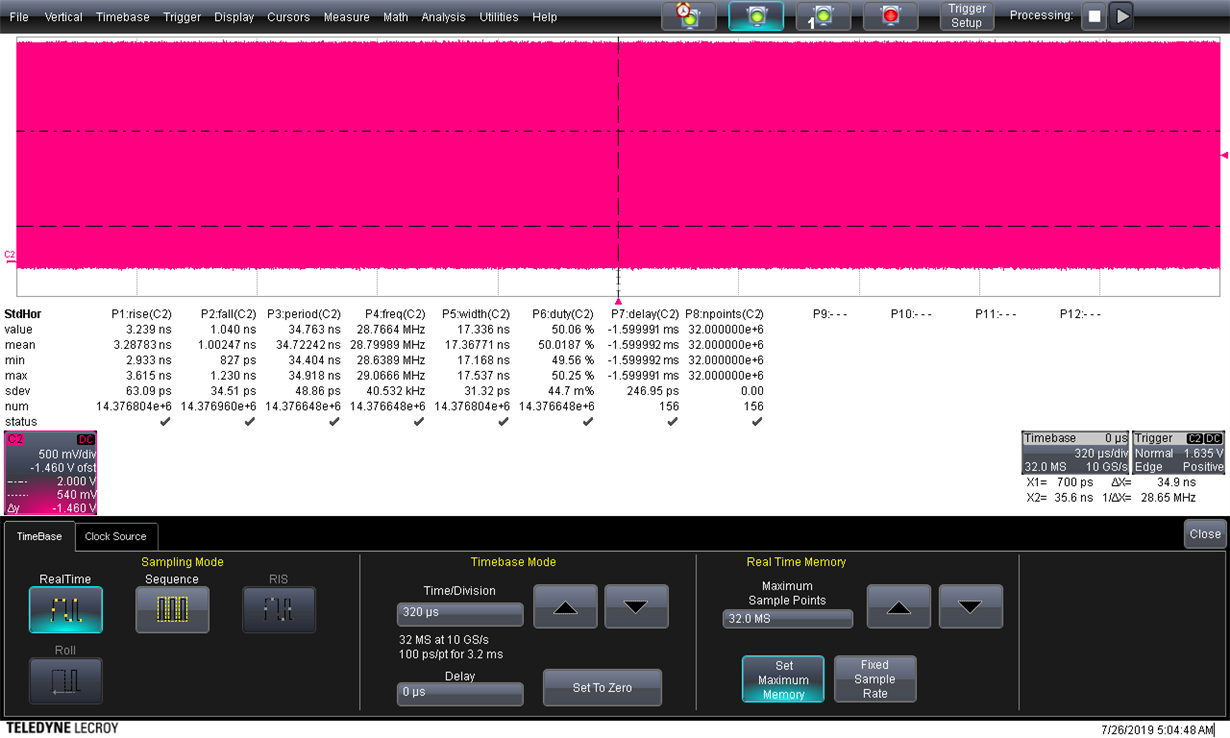

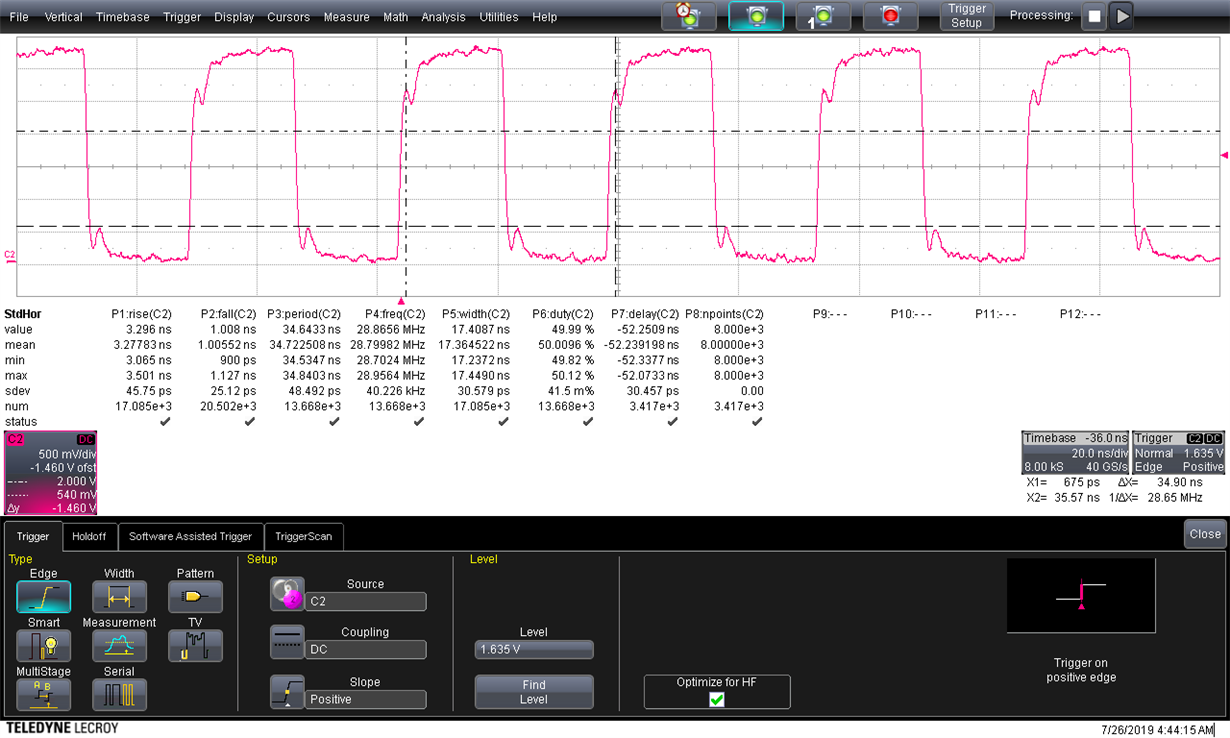

SN65LV1224B 和 SN65LV1023A 位于同一 PCB 上、并从由 嵌入式 PLL 提供的两个独立 FPGA IO 接收其 REFCLK。 频率为28M8Hz。

在两个器件之间的连接中、发送器侧的每个信号线路中都有一个33欧姆电阻器、接收器侧的+和-信号线路之间有一个100欧姆电阻器。

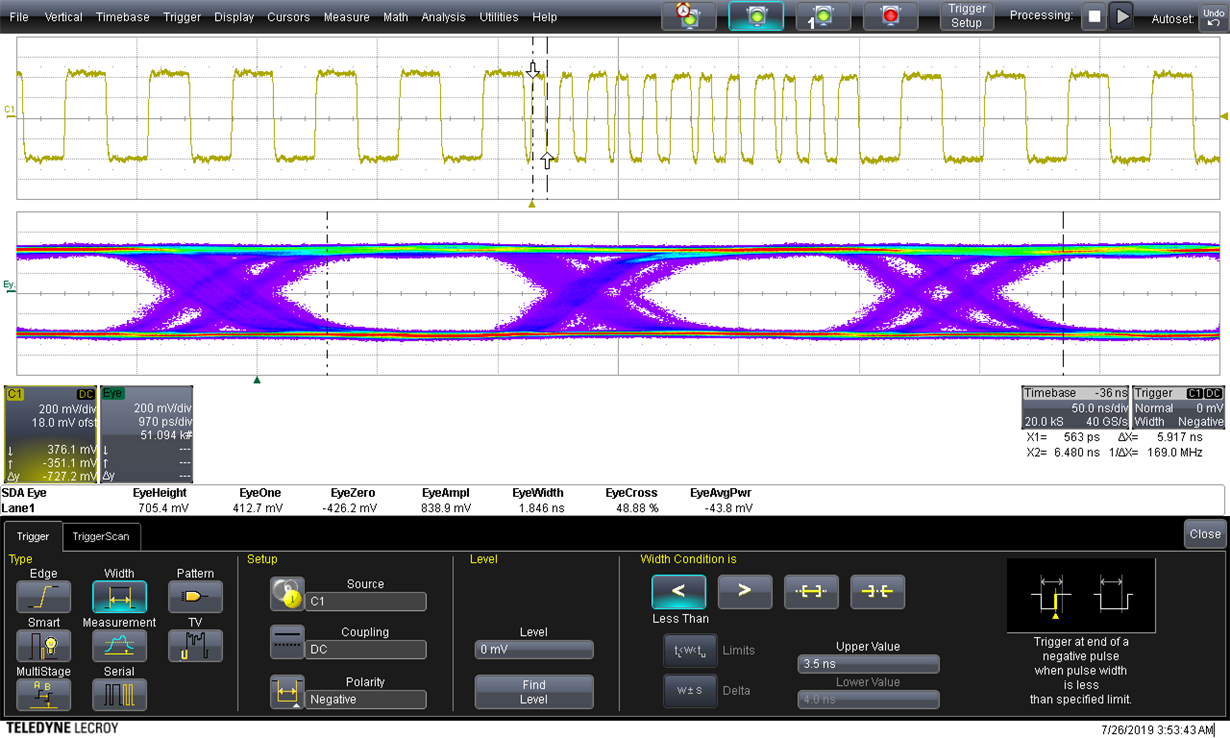

当我使用回路电缆时 、SN65LV1224B 无法锁定。

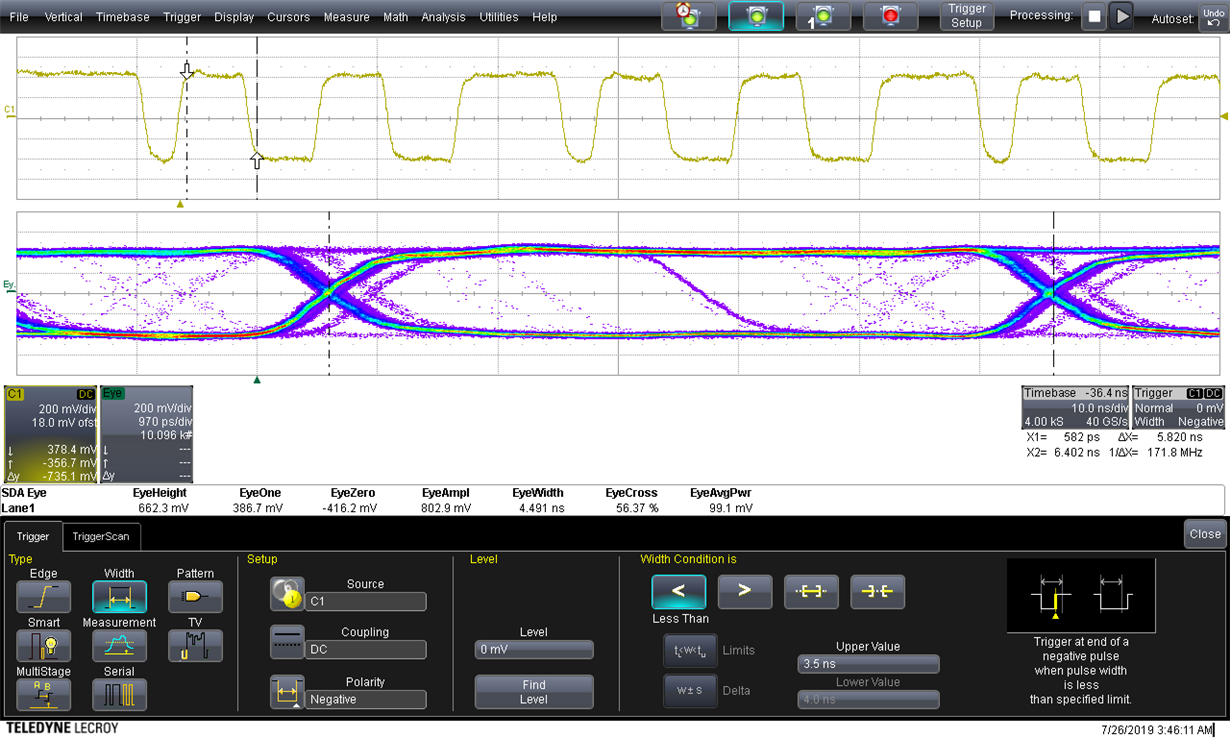

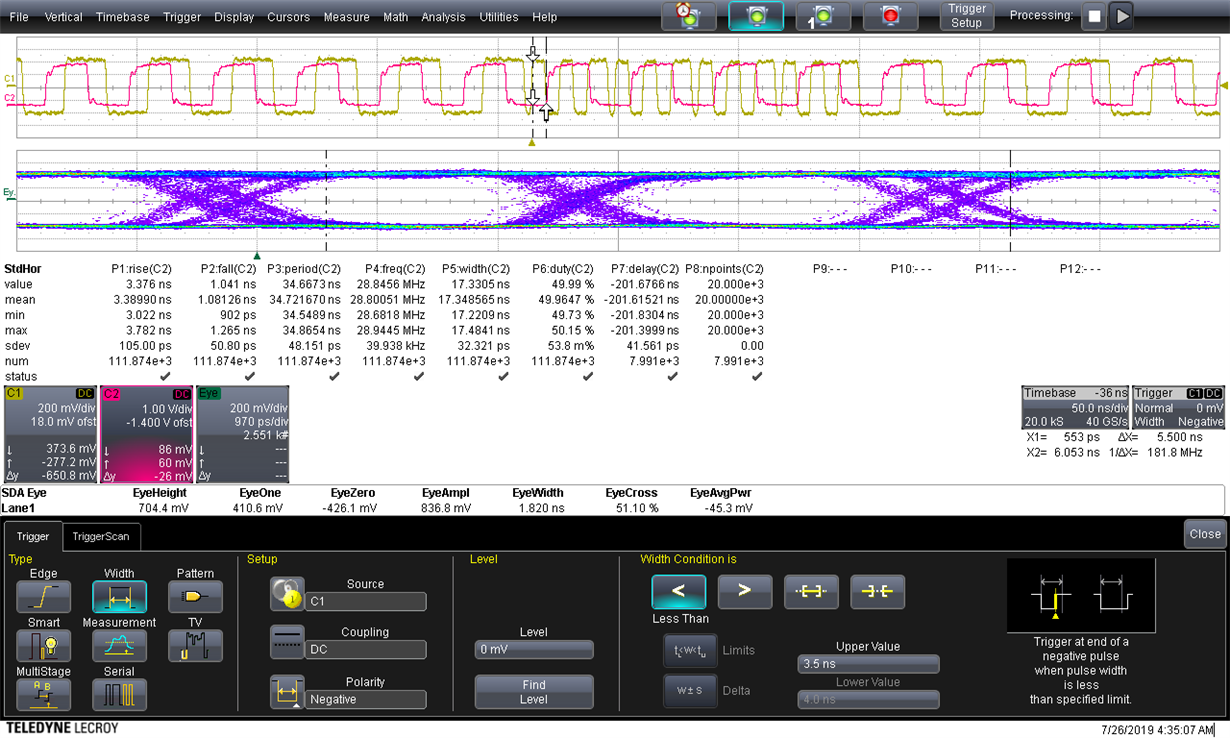

添加连接到 Teledyne / LeCroy SDA 808ZI-A 示波器的差分探头(LeCroy WL-plink + D830和 DXX30-SP)、SN65LV1224B 锁定并正确接收传输的数据。 即使示波器已关闭但仍连接到电源、锁定仍保持、且接收到的数据等于发送的数据。 当探头从示波器上断开并保持在电路板的 GND 时、一切工作正常。

问题可能出在哪呢?

基准时钟似乎可以、因为可以锁定。

发送的 SN65LV1023A 数据 正确。 当连接到 DS92LV1212A 时、器件会锁定并正确传递数据。

在电路板的上一版本 中、串行器:DS92LV1021A 和解串器:DS92LV1212A 的使用没有任何问题。

Thx