我们使用 PCA9545 I2C 端口扩展器芯片。

在我们的应用中、我们使用8个数字 I/O 线路作为输入(也可通过软件编程)。

有时、我们不知道何时以及为什么一个或多个输入会损坏或无法正常工作。

发生这种情况时、无法读取这些输入引脚的状态、通常我们会看到该输入损坏时为高电平。

我们正在寻找此故障的根本原因,但我们目前还无法解决。

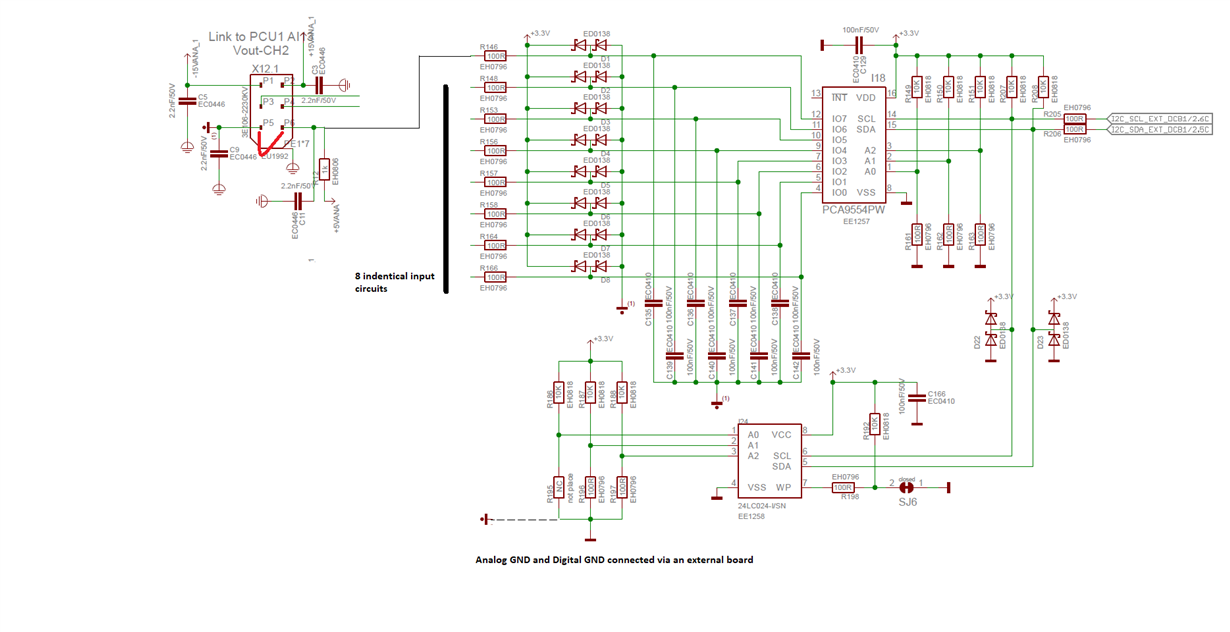

我们在数字输入端提供了以下不准确的电路设计:

在所有这些数字输入之前、我们在每个引脚上使用一个 RC 低通滤波器。

这些电路板的设计人员将1.1k Ω 至+5V (当它变为高电平时)和100 Ω(当它变为低电平时)以及100nF 的电容接地。

IO0上端口引脚的上升和下降时间. IO7很高,太高了,我想..

- 端口引脚 IOX 的上升时间::τ= R * C -> 1.1k Ω* 100nF = 110uS

- 端口引脚 IOX 的下降时间:Tau = R * C -> 100Ohm * 100nF = 10uS

我想 CMOS 输入电路的上升和下降时间不能超过100ns…1us (最大值),而不是电子产品系列中的通用知识,这是更未知的,否则应使用施密特触发输入。 遗憾的是、该最大值 数字 I/O 引脚的上升和下降时间无法在数据表…中找到。

我向 TI 的应用工程师和社区提出的问题:

您是否认为在我们的应用中、通过以超过50us 的高上升时间驱动这些输入来破坏输入电路的合理性?

可以计算 TTL 低电平和 TTL 高电平之间危险区域的上升时间:

TAU = 110us --> 来自最大值 将0.8V 的 TTL 低电平更改为2.0V 的最小 TTL 高电平--> 我想说,在转换期间,Tau 的一半是正确的值--> 所以我认为它超过50us