主题中讨论的其他器件:TMS320F28388D

你(们)好。

我是 Dave、是初级硬件工程师。

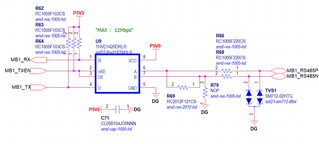

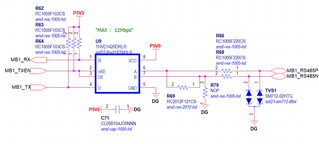

首先、我设计了如下 RS485原理图。

但当我想与其他器件(我不知道原理图)通信时、

我已将电源(24V)、GND、RS485_A、RS485_b 连接到其他器件。 (我的板为其他器件提供24V 电源)

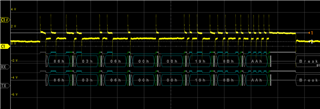

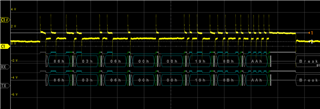

如下图所示。

我能不能知道为什么是 Glich(?) 它就像这样降低电压电平一样?

感谢你的答复。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好。

我是 Dave、是初级硬件工程师。

首先、我设计了如下 RS485原理图。

但当我想与其他器件(我不知道原理图)通信时、

我已将电源(24V)、GND、RS485_A、RS485_b 连接到其他器件。 (我的板为其他器件提供24V 电源)

如下图所示。

我能不能知道为什么是 Glich(?) 它就像这样降低电压电平一样?

感谢你的答复。

您好、Dave、

您要在上面的示波器快照中测量哪个引脚的电压?

此外、它看起来好像 TX 信号和 RX 信号是匹配的-除非我对其进行了误读-这意味着器件似乎正在通信。

您是否担心信号的过冲/下冲? 这可能是由电路板/电缆上的寄生电容引起的、也可能是由于阻抗不匹配导致的-即、如果阻抗不匹配、则这些点之间的任何边界处的电路板到电缆之间的任何边界都会反映能量-我假设这种情况至少在一小段时间内发生 因为数据信号中存在一些纹波。

两个电路板之间的电缆长度(如果有电缆)、电路板上布线的特性阻抗以及电缆的特性阻抗是多少? 我想、由于串联电阻器、存在固有的失配(最好移动串联电阻器、以便端接为我们看到的第一个"负载"-因为这将更容易实现阻抗匹配、并且仍然提供相同的优势。 一般来说、如果以我认为您的系统的点对点方式进行配置、那么正确的 RS-485系统 另一个系统应被视为120欧姆差分负载-如果不是这样、如果没有更多信息、则很难实现阻抗匹配-但 RS-485标准将此作为基准。

请告诉我!

最棒的

Parker Dodson

您好、Dave、

在该实现中、收发器将正常-但我担心 MCU 损坏(除非它具有5V 容差输入)、因为"R"引脚将输出接近5V、如果 MCU 不能承受5V 电压、则可能会损坏 MCU。 R 引脚上必须存在5V 至3.3V 的电平转换器-这可以通过分立式或电平转换 IC 来实现。 D、DE 和/RE 引脚可被拉至3.3V、因为这大于 VIH (max)、所以逻辑1和0仍可通过 、并且由于 VCC 为5V、因此收发器不会因3.3V 信号而受损。

如果您有任何其他问题、请告诉我。

最棒的

Parker Dodson