Other Parts Discussed in Thread: LMH0031, THS8200-EP, THS8200, TVP7002

主题中讨论的其他器件:LMH0031、 THS8200、 TVP7002

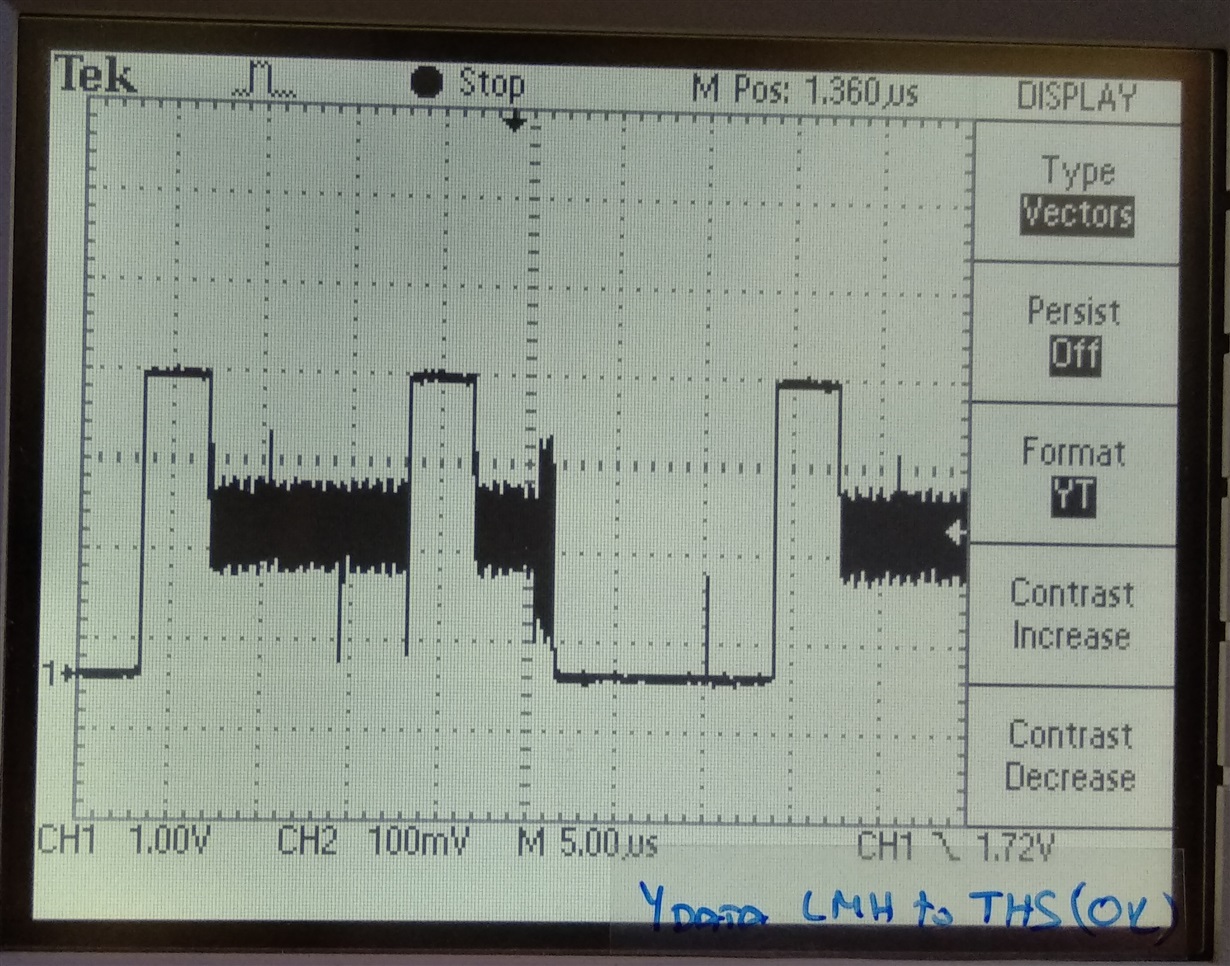

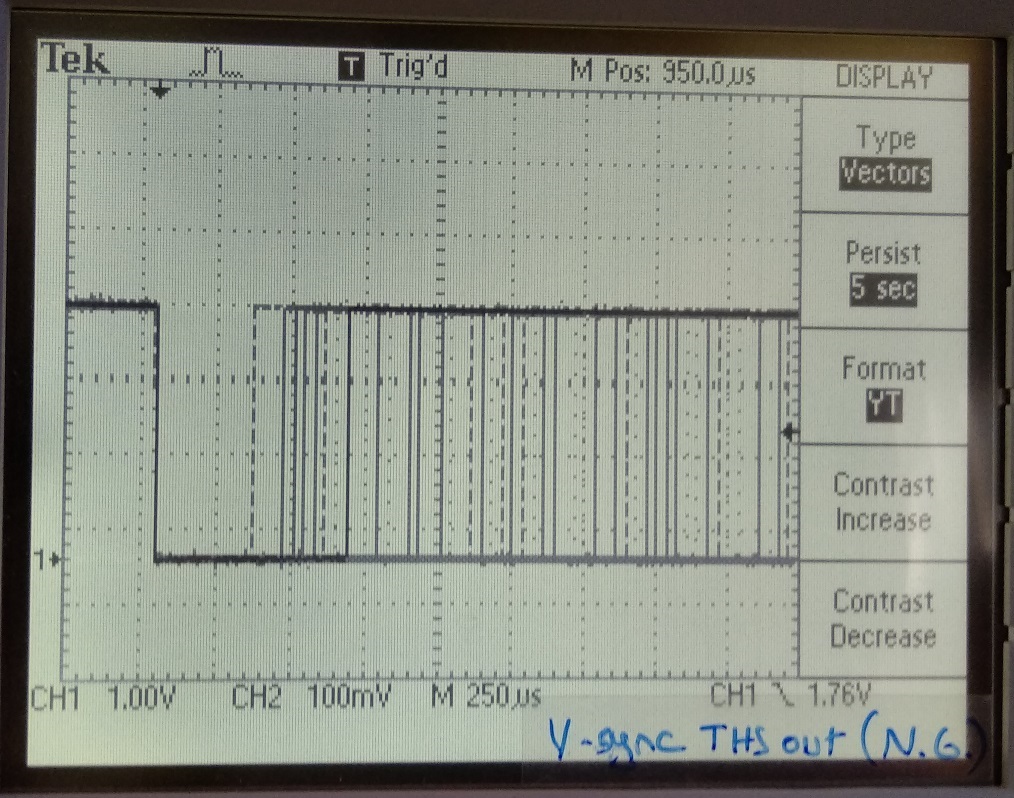

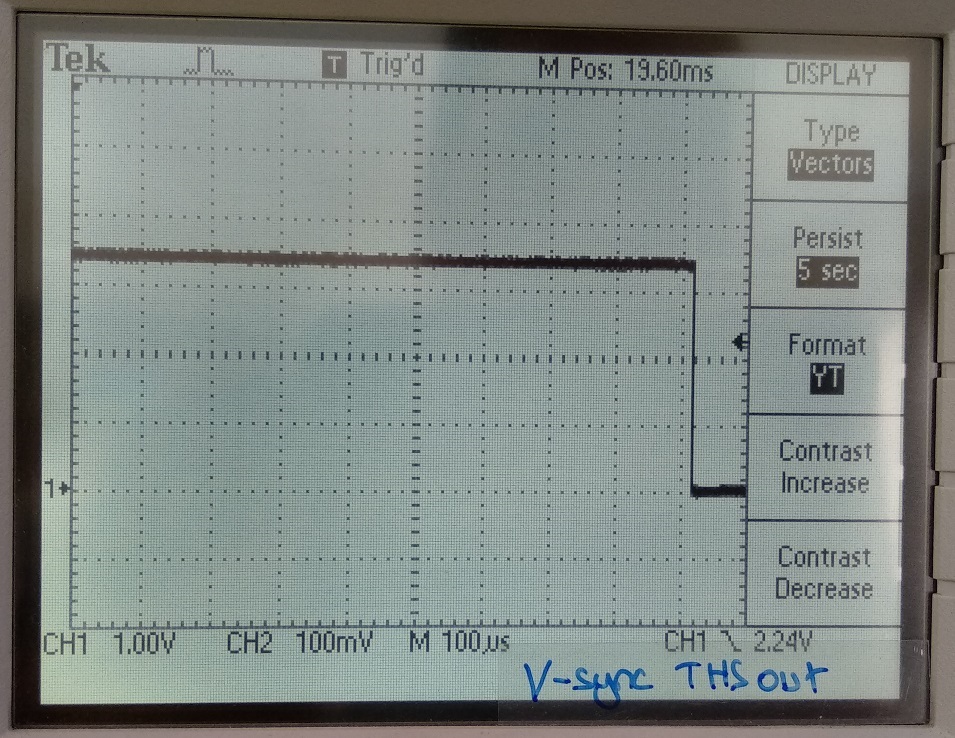

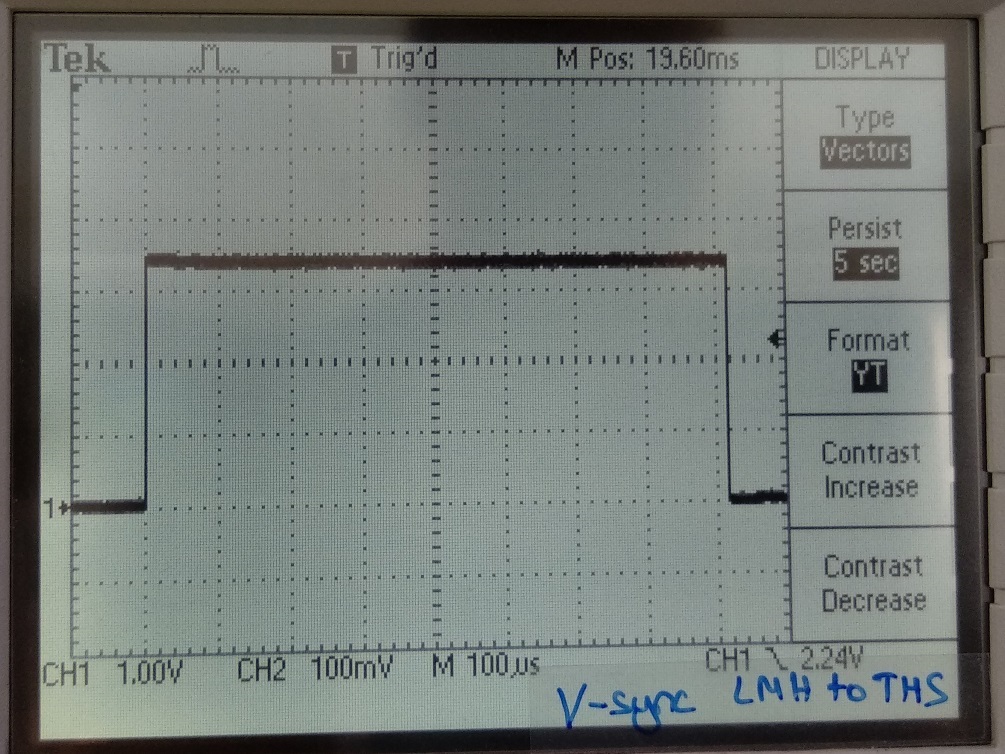

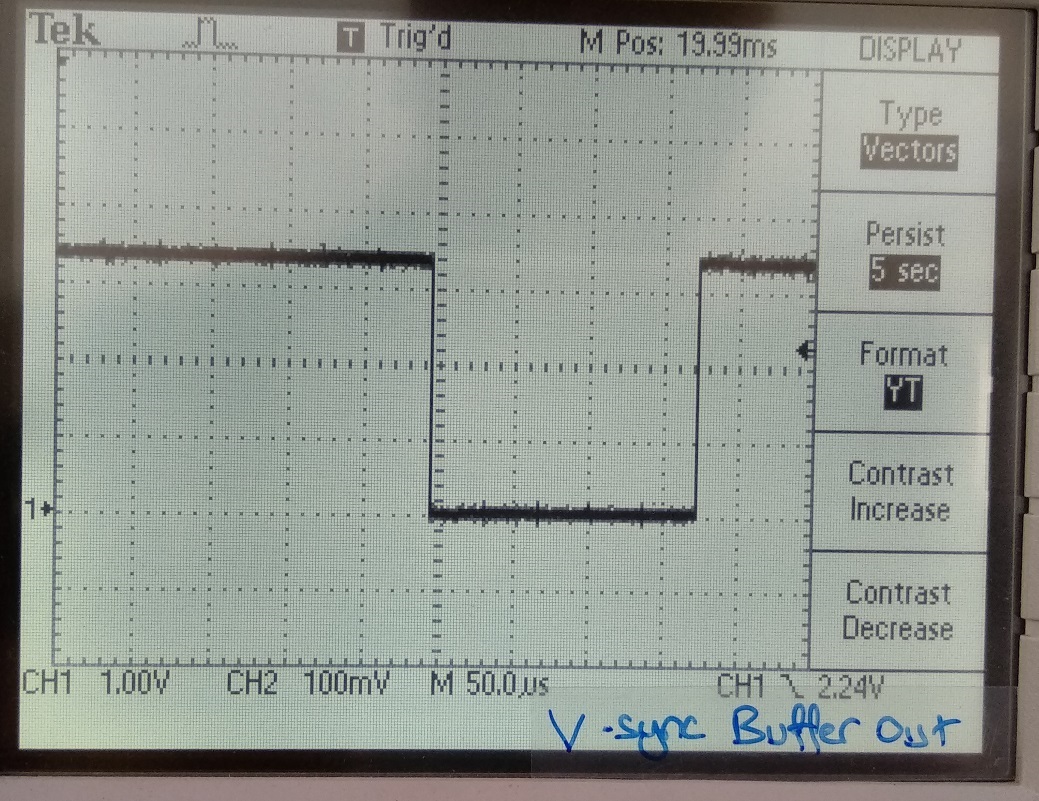

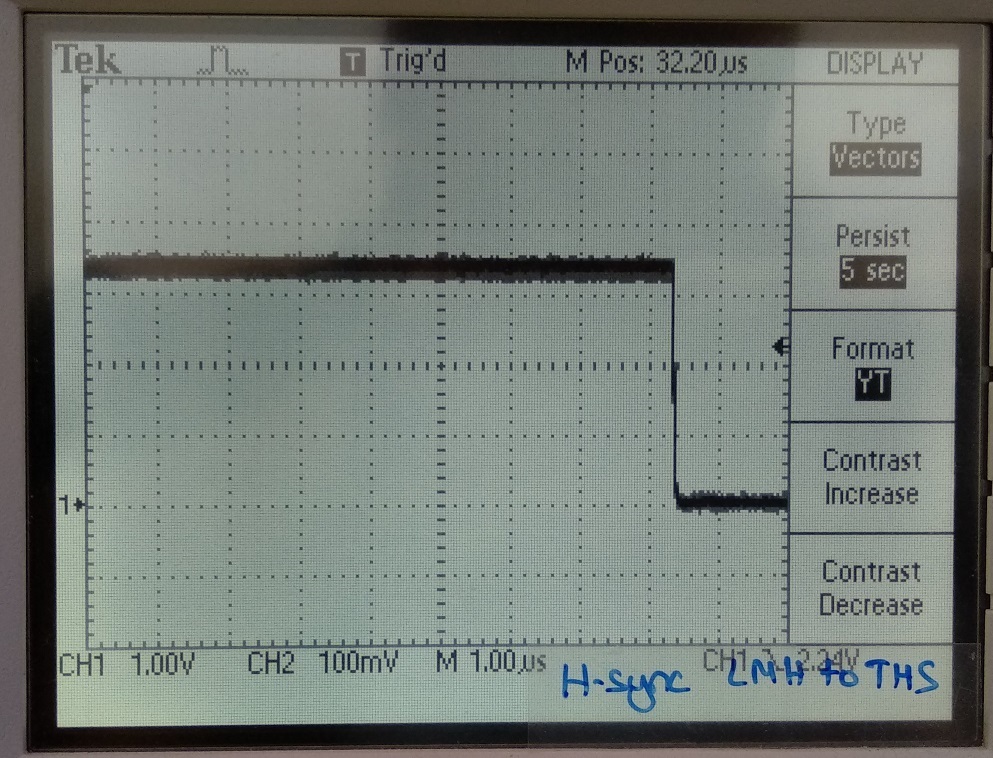

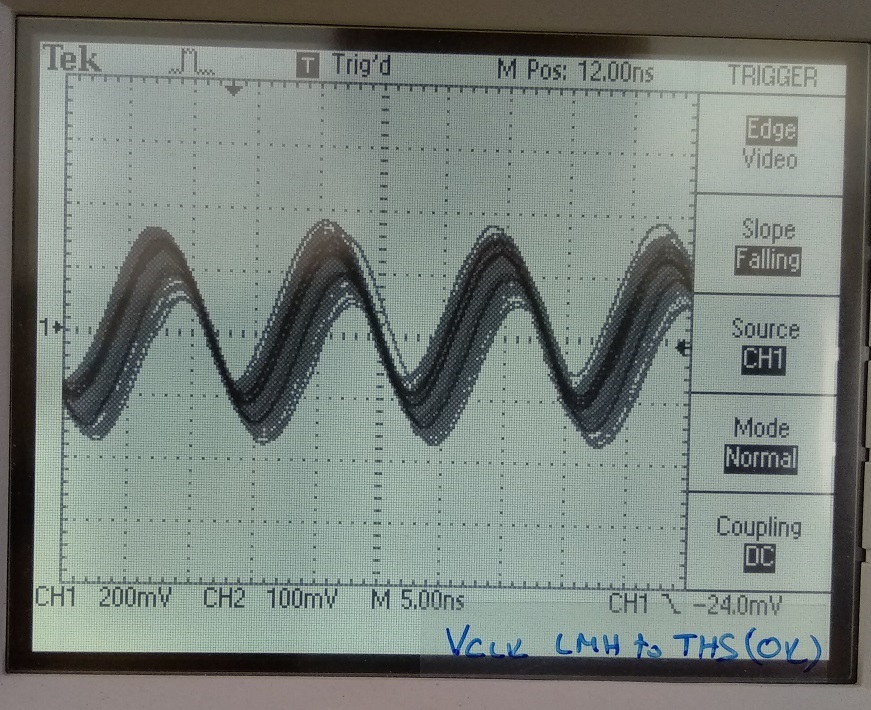

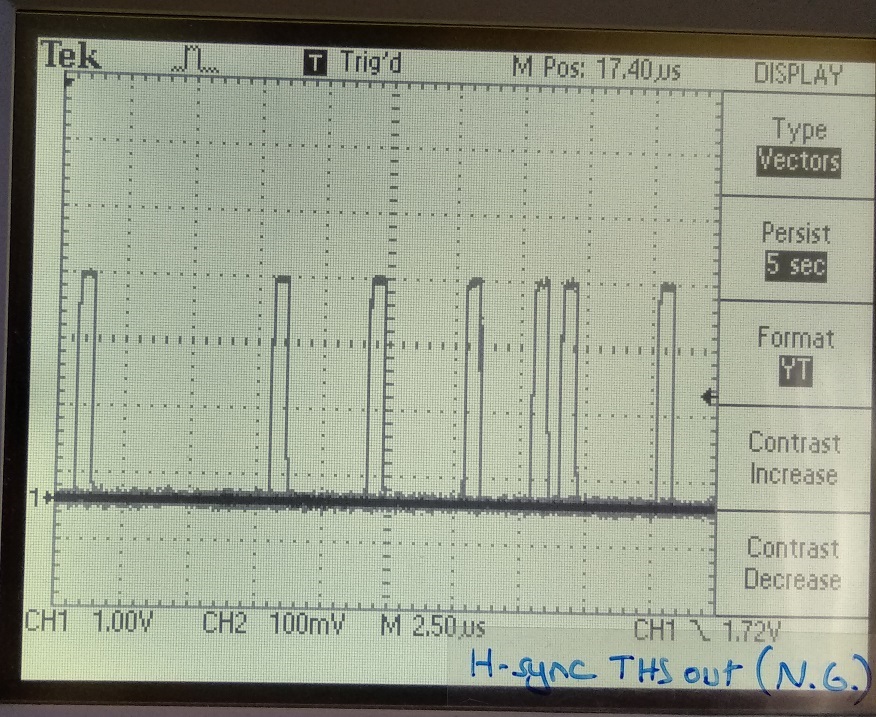

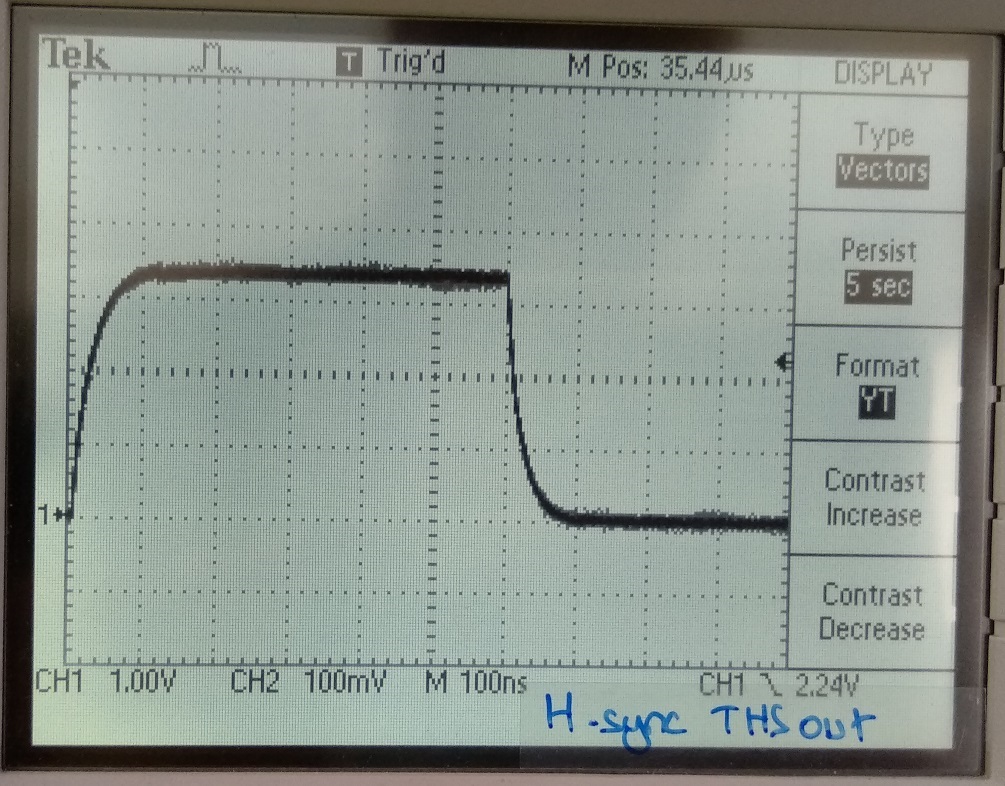

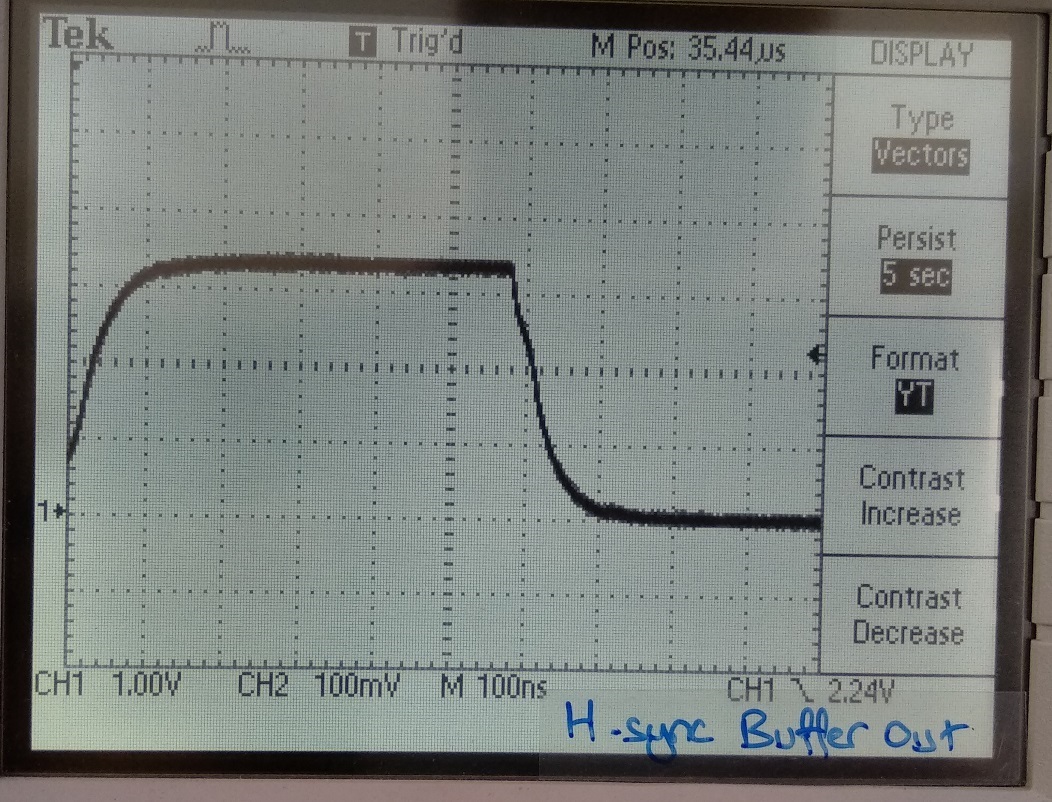

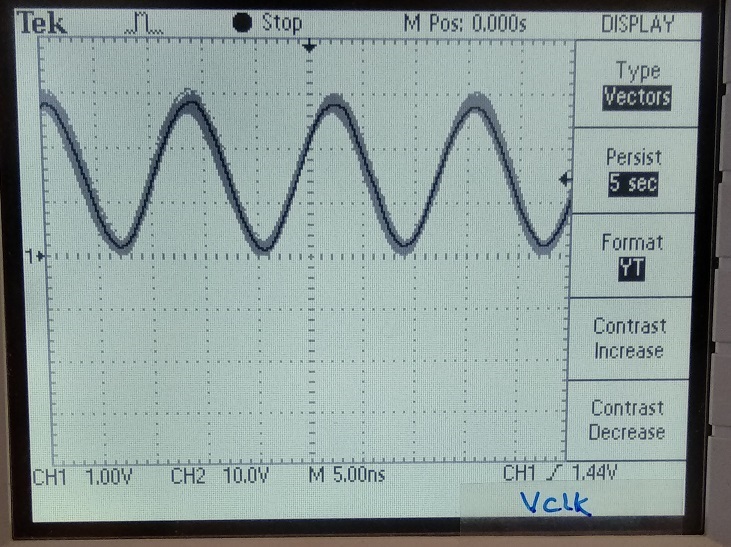

我 正在从事一个 HDSDI 至 VGA 转换器项目。 由于 Hsync 或 Vsync 脉冲不规则、VGA 显示器无法感应输入格式。 RBG ADC 输出正常。 HSYNC OUT 和/或 VSYNC OUT 并不 总是锁定到输入信号。 随机出现问题、锁定后 保持正常运行、不会改变输入信号或打开电源。THS8200-EP 的源为 LMH0031。 20位视频数据,HS、VS、F 连接至 THS8200-EP。 设置 DS 和 ES 的结果相同。 LMH0031的 HS 和 VS 始终正常。