大家好、

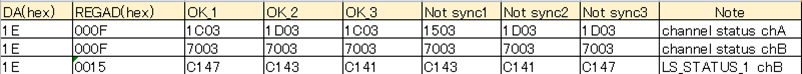

我的客户面临的问题是、在 TLK10232上发出数据路径复位时 FPGA 遇到了某个时间停滞。 在我们检查 FPGA 错误状态时、似乎 FPGA 在时序上的 XAUI 线路上出现对齐错误、并且由于某种原因无法再次同步。

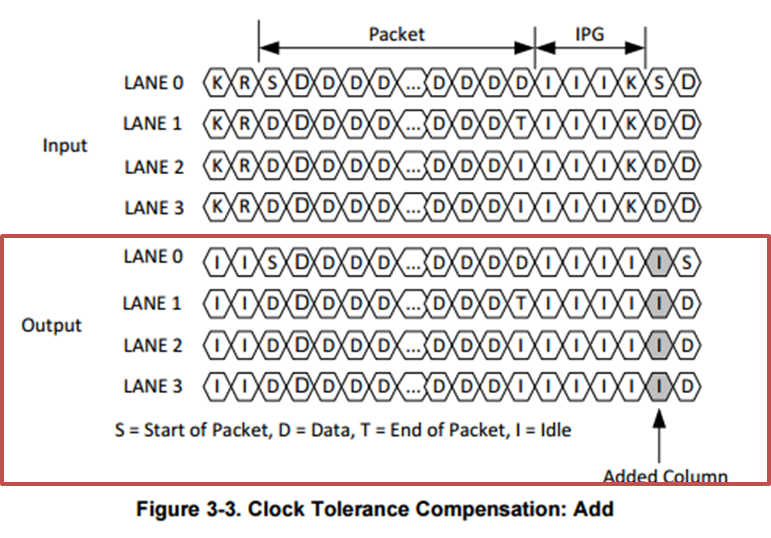

根据数据表、TLK10232自动将/A/、/K/和/R/字符转换为空闲字符、并且在 XAUI 线路上持续输出"空闲"模式(数据包之间)。 我们猜测这可能是此问题的根本原因。

是否有任何寄存器可为 XAUI 通道对齐发出字符?

客户在10G KR 模式下使用 TLK10232、因此 FORCE_LM_REALREALGY 寄存器更改不起作用、因为该寄存器仅适用于10G-KX 模式。

(我认为可以使用 PCS_RX_DEC_CTRL_CHAR、所以如果您知道该寄存器的行为、请告诉我。)

此致、

Takashi Onawa