您好!

我对 TUSB4020BI GRSTz 输入规格有几个问题。 时序技术规格是、在 GRSTz 置为无效之前、VDD (+1.1V)和 VDD33 (+3.3V)必须在3ms 内保持稳定。

问题1:即使 GRSTz 引脚随后在上电后置为有效并置为无效、也必须满足该时序规格? 如果在加电时不符合规格、会发生什么情况? 我们拥有处理器对此复位引脚的控制、如果需要、我们可以为其提供复位脉冲。 或者、如果不满足上电复位时序、集线器是否会进入危险状态(闩锁等)?

该技术规格规定、在2个电源电压稳定后、GRSTz 必须保持低电平3ms。 对这一点的严格解释是:

- 对于电源电压,“稳定”意味着每个电源都达到其最终电平,而不仅仅是接近该电平的某个电平。还是达到最终值的90%?

- GRSTz 必须在3ms 窗口内处于或低于其 VIL 规格+其最小迟滞规格。 VIL 为0.8V、但输入迟滞没有最小规格、因此我必须假设它为0。 因此、在两个电压都稳定后的3ms 内、GRSTz 不得超过0.8V。

问题2:这是正确的吗? 或者、该规范是否真的规定 GRSTz 在两个电压稳定至少3ms 之前不得超过 VIH?

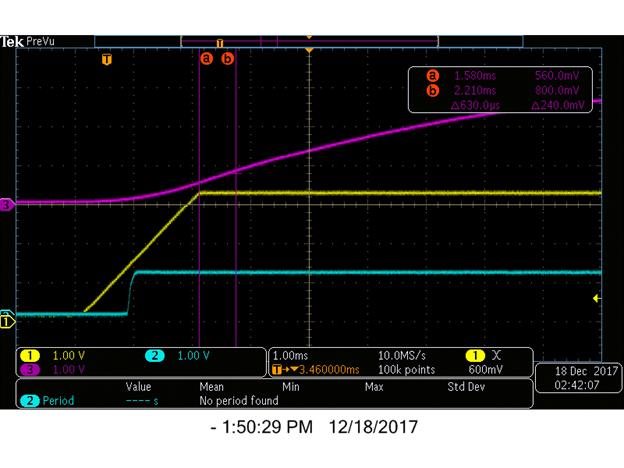

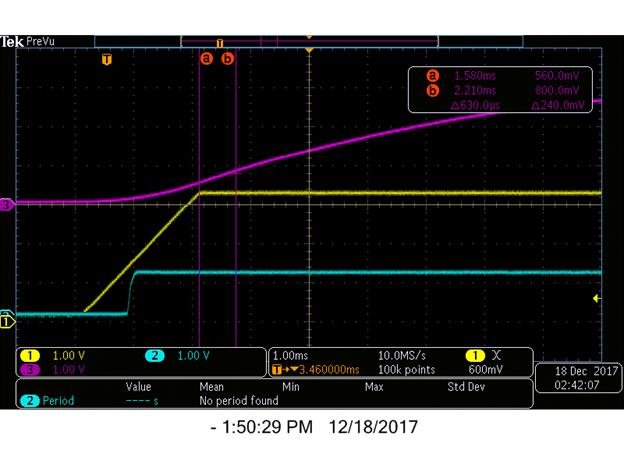

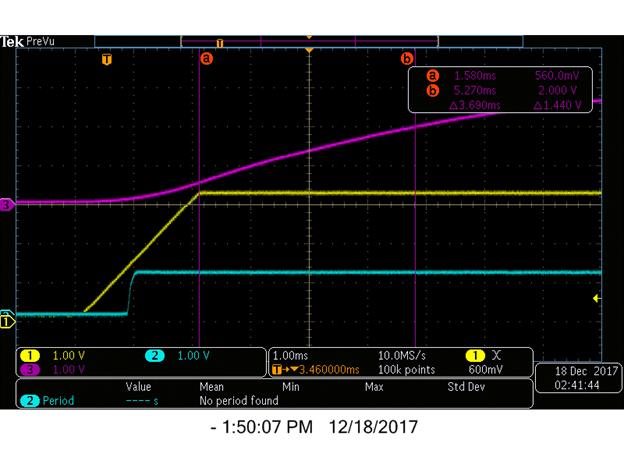

作为参考、下面是示波器捕获(稳定至 GRSTz=0.8V 和 GRSTz=2.0V 的电压)。 在这种情况下、集线器功能正常、但为了严格解释规范(0.8V)、在电源电压稳定后、复位仅为低电平0.44ms。

通道1:VDD33

通道2:VDD

CH 3:GRSTz

谢谢、

Rohit Joshi