请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:DP83822IF 大家好、

我的客户正在使用我们的 DP83822。 他们使用 FPGA 实现 Mac 功能。 下面是您的支票4件/板的原理图。

e2e.ti.com/.../RP4032_2D00_1_2D00_001-_5F00_-p04_2D00_PHY.pdf

它们使用 RMII 和50MHz osc 基准。

问题在于:

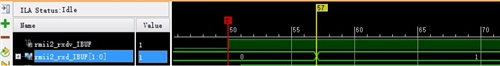

调试 DP83822时、发现 PHY 的 RXDV、RXD[1:0]时序可能有一些问题:RXDV 信号之后、RXD[1:0]信号将在7 clk (约140ns)后输出。 请参阅以下时序图:

这些是 RXDV 消息末尾的突然变化、见下面:

客户正在推动 pp 计划、所以您能帮您检查以上2个问题、非常感谢!

此致、

Sulyn